10nmプロセス以降に焦点、“微細化のその先”も:「2016 VLSI Symposia」プレビュー(1/2 ページ)

2016年6月に米国ハワイで開催される「2016 VLSI Symposia on VLSI Technology and Circuits」では、10nm以降のプロセス技術の研究成果も多数発表される予定だが、“微細化のその先”についても、これまで以上に活発な議論が行われるようだ。

「半導体技術の進歩が難しくなり市場をけん引する要素が多様化するのに伴って、半導体のロードマップも変化している」―――。これは、2016年6月に米国ハワイで開催される半導体技術の年次イベント「2016 VLSI Symposia on VLSI Technology and Circuits」でのメッセージだ。

「2016 VLSI Symposia」では、プロセス技術を10nm以下に微細化するための革新技術に関する論文が220本以上発表される予定だ。さらに、IoT(モノのインターネット)の消費電力を削減する回路技術や車載エレクトロニクス、ビッグデータの分析に関する論文も350本発表されるという。

同イベントの本会議は、時代の変遷がはっきりと感じられる内容になっている。

IntelやIBM、GLOBALFOUNDRIESといった企業の専門家によるパネルでは、「More Moore, More than Moore or Mo(o)re Slowly」と題したセッションで半導体の微細化の減速やその影響について議論が交わされる予定だ。また、別のパネルでは、「Semi Business beyond Scaling(微細化の先にある半導体ビジネス)」についても議論される。

「Symposium on VLSI Technology*)」の実行委員長を務めるRaj Jammy氏は、プレスリリースの中で「平面での微細化は限界に近づいている。そのため、半導体業界は、3次元IC、組み込みメモリ、SiP(System in Package)において微細化が進んでいくだろう」と述べている。

*)2016 VLSI Symposiaは、「Symposium on VLSI Technology」と「Symposium on VLSI Circuits」の2部構成のイベントとなっている。

プロセス技術戦略を変えたIntel

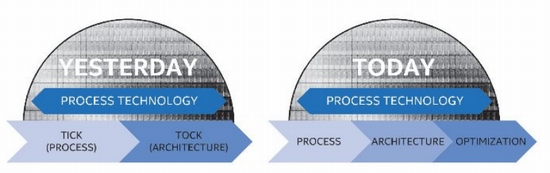

実際に、Intelは有価証券報告書「Form 10-K」の中で、1つのプロセスを適用する期間を延長することをひっそりと認めている。

同社は、14nmプロセスと同様に10nmプロセスを、3世代のプロセッサに適用する計画だという。これまでは、1つのプロセスを2世代のチップに適用し、2年ごとに新しいプロセスノードを導入してきた。

Intelは、「現行の14nmと次世代の10nmプロセス技術を適用する期間を延長し、毎年の市場変化に対応した製品を投入できるように、製品とプロセス技術の最適化にさらに注力する計画だ」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.