0.03μm2のSRAMから最先端のIII-V族FinFETまで:「VLSI技術シンポジウム 2016」プレビュー(2/5 ページ)

米国ハワイで2016年6月13〜16日に開催される「VLSI Symposia on VLSI Technology and Circuits(以下、VLSIシンポジウム)」は、最先端の半導体デバイス/回路技術が一堂に会する国際会議だ。VLSIシンポジウムを実行するVLSIシンポジウム委員会は4月20日、都内で記者説明会を開催し、同イベントの概要と注目論文を紹介した。

技術シンポジウムの注目論文

85件の採択論文のうち、最も多いのはプロセス技術で27件。次にメモリ(23件)、先端CMOS技術(14件)、CMOS移行/新技術(8件)と続く。記者説明会では、VLSI技術シンポジウム プログラム委員長の昌原明植氏が、注目すべき論文を幾つか紹介した。

10nm以降のプロセス技術

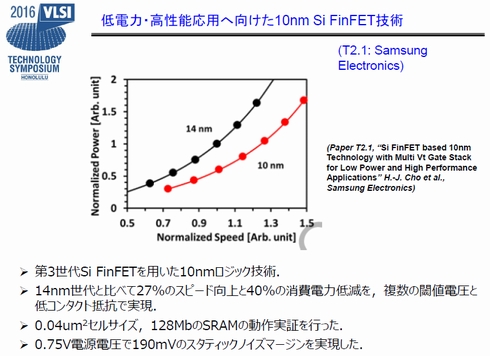

まずはSamsung Electronicsが発表する、10nmプロセスを用いたシリコンFinFETだ。14nm世代のFinFETに比べ、27%のスピード向上と、40%の消費電力削減を、複数の閾値電圧において実現したという。セルサイズは0.04μm2で、これを128MビットのSRAMで動作実証している。さらに、電源電圧を0.75Vまで下げてもスタティックノイズマージンが190mVと、高い動作安定性を実現していることが特長だという。

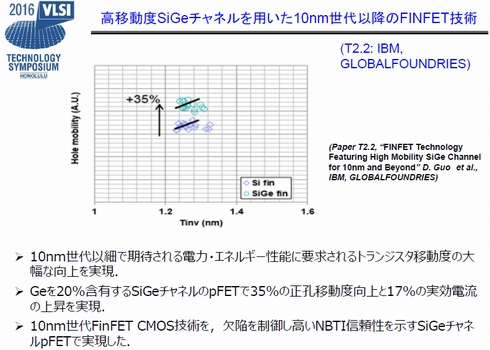

IBMとGLOBALFOUNDRIESは、SiGe(シリコンゲルマニウム)をチャネルに用いた、10nm世代以降に使用できるFinFET技術を発表する。Geを20%含有するSiGeチャネルのp型FET(絶縁膜の厚みは1.2〜1.3nm)で、正孔移動度が35%向上し、実効電流が17%上昇したとする。昌原氏は、「SiGeを使うと欠陥が多くなるが、そこを制御して高い信頼性を確保したことがポイントだ」と説明した。

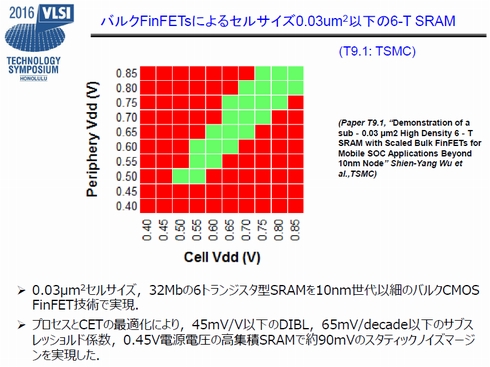

TSMCは、セルサイズが0.03μm2で32MビットのSRAM(6トランジスタ型)を、10nm世代のバルクCMOS FinFETで実現した。0.45Vの電源電圧で約90mVのスタティックノイズマージンを実現したという。

Copyright © ITmedia, Inc. All Rights Reserved.