ニュース

室温でグラフェン回路をフレキ基板上に形成:シャドーマスクを使用(2/2 ページ)

米大学の研究チームが、室温環境でフレキシブル基板上にグラフェン回路を形成する技術を開発した。

課題は微細化か

現時点では、Yong氏らの方法を用いて製造されたグラフェンチップの大きさに限度はないが、シャドーマスクをどれほど細かくエッチングできるかという点では限界がある。現在のシリコン回路は既にナノメートル領域にあるが、シャドーマスクプロセスはマイクロメートル領域にとどまっている。そのため、シャドーマスクプロセスでシリコン加工を仕上げるにはいまだ課題がある。

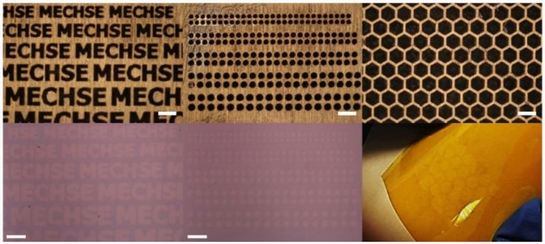

上=精緻なミクロン規模の機能を備えたさまざまなステンシルマスクの光学顕微鏡画像 / 下=柔軟性のあるカプトン膜上に移された対応するグラフェン層のパターン (クリックで拡大) 出典:University of Illinois, Urbana-Champaign

50μmを実証

Yong氏は「われわれはこの簡易なアプローチを用いて、線や文字、円などが含まれたさまざまなグラフェン層のパターンを50μmまでの異なるサイズで実現できることを実証した」と語った。

Yong氏によると、研究者らは今後、シャドーマスクを縮小し、実デバイスを構築することで、現在必要とされる数十億米ドルよりも安い、数千米ドルをかけてラボを装備すれば、実用的なグラフェン回路を製造できるようになるというアイデアを証明するという。

研究チームには、博士研究員のPilgyu Kang氏や、既にイリノイ大学を卒業し、現在はIntelに勤務しているAli Ashraf氏なども参加している。

【翻訳:滝本麻貴、青山麻由子、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

グラフェン+半導体ポリマーの“ハイブリッド素材”、高性能な有機トランジスタ実現の鍵に

グラフェン+半導体ポリマーの“ハイブリッド素材”、高性能な有機トランジスタ実現の鍵に

スウェーデンの大学とスタンフォード大学が、単層グラフェン上に半導体ポリマーが形成された“ハイブリッド素材”を開発。シリコンに匹敵する性能を持つ有機トランジスタの実現にまた一歩近づいた可能性がある。 グラフェンの超伝導化に成功、東北大学など

グラフェンの超伝導化に成功、東北大学など

東北大学原子分子材料科学高等研究機構(AIMR)の高橋隆教授らによる研究グループは、グラフェン(黒鉛の単原子層)の超伝導化に成功した。「質量ゼロ」の電子を「抵抗ゼロ」で流すことが可能となるため、超高速超伝導ナノデバイスなどへの応用開発に弾みが付くものとみられる。 「シリコンもグラフェンも超える」、新たな半導体材料をスイスの大学が発表

「シリコンもグラフェンも超える」、新たな半導体材料をスイスの大学が発表

二硫化モリブデンは、二次元方向に広がる層状の結晶構造を備えているため、結晶構造が3次元のシリコンよりも、膜状に加工しやすい。さらにバンドギャップを備えているためにグラフェンよりも扱いやすい。 分子磁気メモリが可能か、グラフェンで

分子磁気メモリが可能か、グラフェンで

スペインとフランスの複数の研究者が、グラフェンと水素原子を用いて、原子サイズの「炭素磁石」を作ることに成功した。紙の上に絵を描くように、グラフェン膜上に磁気パターンを作り出すことができる。分子磁気メモリやスピンを利用した通信につながる成果だ。