IBM、3ビット/セルのPCMの研究成果を発表:100万回の耐久性試験を実施(1/2 ページ)

IBMチューリッヒ研究所が、3ビット/セルのPCM(相変化メモリ)の研究成果を、パリで開催された「IEEE International Memory Workshop(IMW 2016)」で発表した。

IBMが、3ビット/セルの4M-Cell(32Mビット相当) PCM(相変化メモリ)アレイの研究成果を発表した。高温環境下で100万回の耐久試験を行ったあとも3ビット/セルでデータを保持することができたという。

スイスにあるIBMチューリッヒ研究所(IBM Research-Zurich)で不揮発メモリ研究担当マネジャーを務めるHaralampos(Haris) Pozidis博士とその同僚たちが、2016年5月15〜18日(現地時間)にフランス・パリで開催された「IEEE International Memory Workshop(IMW 2016)」において、その詳細を初めて明らかにした。

IBMが今回実現した3ビット/セルPCMの可能性をどのような言葉で表そうと、その成果が極めて素晴らしいものであることに変わりはない。

同社は今後、3ビット/セルのMLC(Multi Level Cell) PCMの実装面積を、3次元積層したシングルビット/セルのPCMとほぼ同等にして、ストレージクラスメモリだけでなく他のさまざまな用途向けとしても、開発していくようだ。ここでポイントになるのは、MLCフラッシュメモリは、シングルビットデバイスの派生品であり、並行で開発されたわけではないという点だ。

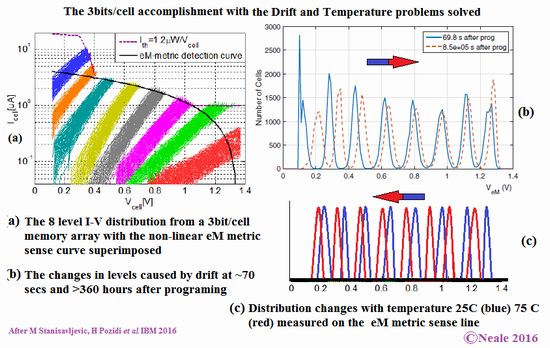

図1(a)は、PCMセルの抵抗分布を8種類、明確に判別できることを示したものだ。ただし、それぞれの抵抗状態を利用するには、図1(b)が示すドリフトや、図1(c)の温度変化などの問題に対処するための手法が必要となる。IBMが今回、これらの問題を解決することができた背景には、次の3つの重要な革新的開発を実現したことがある。ドリフトの影響を受けないセル状態の基準の設定、ドリフト耐性を備えたコーディング、そして検知方法の仕組みである。

IBMはこれまでにも、PCM関連の課題を解決すべく、同社の開発チームがさまざまな技術を適用しながら進めてきた取り組みについて、一部の詳細を明らかにしている。特に、ドリフトや温度変化、書き込み/消去のライフタイムといった問題を取り上げてきた。

IBMの科学者たちは現在、スタンドアロンPCMの他、PCMを超高速キャッシュとして使用しながらフラッシュメモリと組み合わせた、ハイブリッド型アプリケーションなどの構想を描いているという。

Copyright © ITmedia, Inc. All Rights Reserved.