IBM、3ビット/セルのPCMの研究成果を発表:100万回の耐久性試験を実施(2/2 ページ)

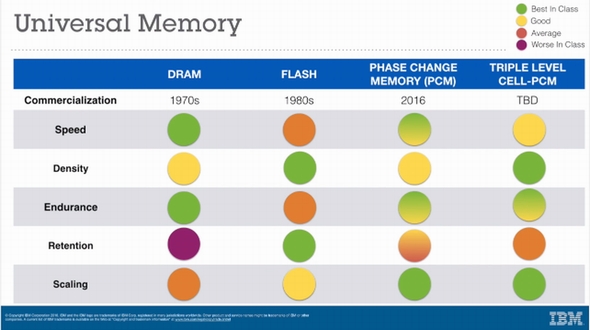

IBMチューリッヒ研究所が、3ビット/セルのPCM(相変化メモリ)の研究成果を、パリで開催された「IEEE International Memory Workshop(IMW 2016)」で発表した。

クロスポイント型メモリについては?

Pozidis氏は、「MLC PCMと、3D(3次元積層)クロスポイント型のシングルビット/セルメモリの主なメリットについてどう考えるか」とする筆者の質問に対し、以下のように答えている。

「3Dクロスポイント技術は、メモリセルとダイオードのレイヤーを積層することをベースにしている。同技術の問題点は、歩留まりにある。各レイヤーの歩留まりが、デバイス全体の歩留まりになる。一方、シングルレイヤーの場合は、このような歩留まりの問題はない。また、マルチビット技術のメリットとして挙げられるのが、3ビット/セルの性能の場合は、1ビット当たりのコストが原理上、3分の1になるということだ。一方で3Dクロスポイントは、2レイヤーであるため、1ビット当たりのコストの低下は2分の1にとどまる」(同氏)。

さらにPozidis氏は、「3ビット/セルまたはマルチビットのPCMを3D構造にするという可能性はあるか」とする筆者の問いに対し、次のように答えた。

「原理上、その可能性はある。TLC(Triple Level Cell)レベルをプログラムするには、プログラムと検証のステップを何度も繰り返すことのできる性能が必要だ。プログラムのステップの中に、セル上の電流を制御する機能が必要になるが、この点については積層構造では問題にならないだろう。アクセス用としてダイオードが何らかの形で使われているためだ。検証ステップについても、問題はないはずだ。ただし、2ビット/セルでは読み出しの際に3つの閾値電圧レベルが必要で、TLCでは7つのレベルが必要になるので、セル状態を比較的正確に測定する必要はある」(同氏)。

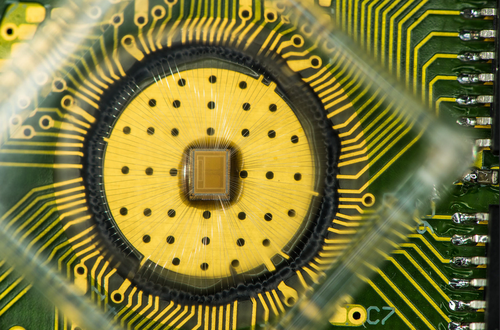

IBMが今回実証に成功したマルチビットPCMの試作チップは、4バンクのインターリーブアーキテクチャを備えた2×2のM-Cellアレイで、メモリアレイの寸法は2×1000×800μmだ。PCMセルは、ドープされたカルコゲナイド合金をベースとし、90nmプロセスのCMOSチップに搭載された。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「3D XPoint」は相変化メモリか――特許から詮索

「3D XPoint」は相変化メモリか――特許から詮索

Intel(インテル)とMicron(マイクロン)がこのほど発表した不揮発性メモリ「3D XPoint」は本当に相変化メモリの1つなのか? 筆者が特許をウェブで検索したところ、この見方を裏付ける結果となった。 IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。 IBMが今後5年間で3000億円を半導体開発に投資

IBMが今後5年間で3000億円を半導体開発に投資

IBMは、7nm以降の半導体微細加工技術と、シリコンに代わる新材料によるチップデバイス技術の開発を主とした研究開発を実施すると発表した。今後、5年間で30億米ドル(約3000億円)を投資するという。