EUVは、微細化の“万能策”ではない:「ITF 2016」で語られた半導体の未来(2)(1/2 ページ)

半導体製造プロセスの微細化を進めるには、EUV(極端紫外線)リソグラフィーが鍵になるといわれている。ばく大な資金が、同技術の開発に投入されているが、その進捗は必ずしも期待通り、予定通りではないようだ。

思うように開発が進まない、EUVリソ技術

鈍化の要因として、多方面、特にEUV(極端紫外線)リソグラフィー技術における多大な努力にもかかわらず、より微細な加工ができる装置が、過去10年にわたりなかなか実用化されずにいることが挙げられる。大手の半導体チップメーカーは、こうしたリソグラフィー技術を開発するために、何十億米ドルもの資金と無数のエンジニアリング時間を投じてきた。

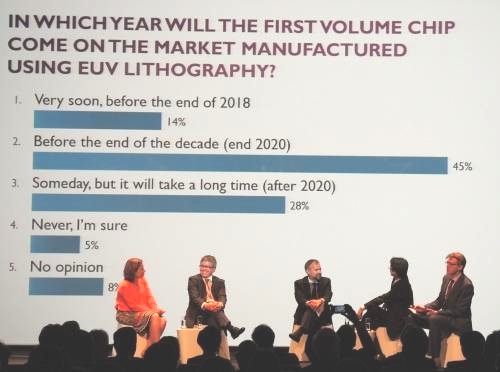

EUVリソグラフィー技術は、2018年にも量産が開始されるとみられている7nmプロセスに合わせて、2020年までのどこかのタイミングで実用化されるというのが、大方の予想である。IMECのプロセス技術部門でシニアバイスプレジデントを務めるAn Steegen氏は、「EUVリソグラフィーの開発は日々進化を遂げている。液浸リソグラフィーでは極めて難しいとされるバックエンドでの複雑なレイヤーが、最初の導入ポイントとなるだろう。これは早ければ早い方がいい」と述べた。

EUVリソグラフィーを早期に導入した他の多くの企業と同様に、IMECも現在、EUVリソグラフィー試作機の光源の出力を80Wにアップグレードしている。チップメーカーらは、チップの量産に必要なウエハー処理能力を実現するには、250Wの光源が必要になる可能性があると指摘する。

Steegen氏は、欠陥率の高さや、レジストのエコシステムの乏しさなど、EUVリソグラフィーが抱える他の課題についても洗い出しを行った。だが、目標とする実用化の時期が迫っている中、半導体製造装置を手掛けるASMLの幹部らは、EUVリソグラフィー技術の進捗を明らかにしなかった。彼らがそれに触れなかったのは、過去数年で初めてのことである。

EUVリソグラフィー技術を支持する業界関係者からでさえ、同技術は万能の解決策ではないという声は聞かれる。EUVリソグラフィーは、一部では、トリプル/クアッドパターニングの必要性を排除するかもしれない。だが工場では、チップをコストダウンするために必要なスループットを得るために、高速液浸ステッパーが必要になるだろう。

それでも、GLOBALFOUNDRIESのCTOであるGary Patton氏は、EUVリソグラフィーは、7nmプロセスのチップの製造時間を30日間も低減できるとした。同氏は、同技術の強力な支持者である。

Copyright © ITmedia, Inc. All Rights Reserved.