FinFETサイズの物理的な限界は?:「ITF 2016」で語られた半導体の未来(3)(2/2 ページ)

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。

FinFETのサイズの限界は?

現在の最先端プロセスの筆頭ともいえるFinFETトランジスタにも、新たな試練は待ち受けている。

IMECのプロセス技術部門でシニアバイスプレジデントを務めるAn Steegen氏は、「FinFETトランジスタの物理的な限界は、高さが約40〜45nm、幅が14〜18nm、奥行きは4〜5nmとみている。同氏は、「その限界を超えると、Fin(フィン)の利点を十分に得ることはできない」と述べ、上記のサイズであれば、ファウンドリーが“7nmノード”と呼ぶであろう範囲にたやすく収まるだろうとした。

Patton氏は、「FinFETから引き出せる能力は、まだまだある。私は、7nmプロセスで真の進歩を見込んでいる」と述べた。同氏は、Intelが開発したような、より高くより薄いFinFETを製造すること以外にも、フロント、ミドル、バックエンド工程で使えそうなテクニックがあると述べた。「試せることは多い」(Patton氏)

SiGeをFinFETに用いる

Patton氏は、GLOBALFOUNDRIESが7nm FinFETにSiGe(シリコンゲルマニウム)を用いる可能性があることを示唆した。このような手法は、同氏がかつて所属していたIBMの研究チームが発表した論文でもテーマになっていた。それ以外にも、Patton氏は、EUVでFinFETの性能を高めることにも見込みがあるという。

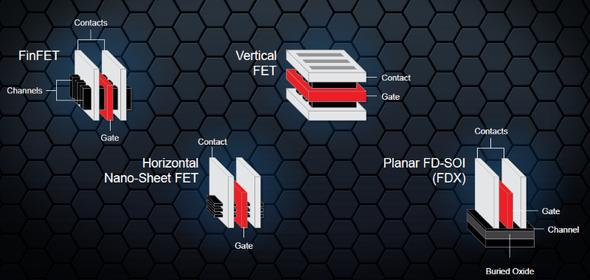

GLOBALFOUNDRIESは、FinFET(左)とFD-SOI(完全空乏型シリコン・オン・インシュレーター、右)以外に、画像中央に示されているような他の技術を用いたトランジスタも開発している(クリックで拡大) 出典:GLOBALFOUNDRIES

プロセスエンジニアたちは、得られる限りの技術が必要になるだろう。7nmプロセスでは、少なくともクアッドパターニングを用いた層が2層、トリプルパターニングを用いた層が複数、必要になると考えられている。Steegan氏は、もしファウンドリーが正しい(微細化の)ピッチを適用すれば、EUVリソグラフィーは大いに役立つだろうと語った。

⇒「「ITF 2016」で語られた半導体の未来」連載バックナンバー

【翻訳:青山麻由子、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

室温でグラフェン回路をフレキ基板上に形成

室温でグラフェン回路をフレキ基板上に形成

米大学の研究チームが、室温環境でフレキシブル基板上にグラフェン回路を形成する技術を開発した。 「ムーアの法則」を超えた進化

「ムーアの法則」を超えた進化

Intelをはじめとした半導体メーカーは「ムーアの法則」に従うように、ほぼ2年に1度のペースで新たな微細プロセステクノロジーを導入し進化を続けてきた。しかし、近年は少しその様子が変わりつつある。特に台頭著しい新興メーカーは、独自のペースで進化を遂げてきている。 パワー半導体、シリコンの置き換えは何年も先

パワー半導体、シリコンの置き換えは何年も先

ドイツで開催されたパワーエレクトロニクスの展示会「PCIM Europe 2016」では、SiCとGaNを用いたパワー半導体が多く展示された。パワーエレクトロニクス業界に40年以上身を置く、ECPE(European Center for Power Electronics)のプレジデントを務めるLeo Lorenz氏に、現在のパワー半導体の動向について話を聞いた。 半導体業界の統合、推進力は規模の経済ではない

半導体業界の統合、推進力は規模の経済ではない

M&Aが続く半導体業界。かつては細分化していった業界を、統合へと向かわせている要因は何なのか。