ルネサス、フィン構造のMONOSフラッシュを開発:16/14nmマイコンへの混載に向け(1/2 ページ)

ルネサス エレクトロニクスが、フィン構造を採用したSG(Split-Gate型)-MONOSフラッシュメモリセルの開発に成功したと発表した。フィン構造としたことで、FinFETなど先端のロジックプロセスとの親和性が高くなり、次世代の16nm/14nm世代マイコンに混載できるようになる。

フィン構造のSG-MONOSフラッシュメモリセル

ルネサス エレクトロニクスは2016年12月7日、16nm/14nm世代以降のマイコン向けに、フィン構造を採用したSG(Split-Gate型)-MONOSフラッシュメモリセルの開発に成功したと発表した。「世界初」(同社)だとする。ルネサスは、米国サンフランシスコで開催中の最先端電子デバイスの国際学会「IEDM 2016」(2016年12月3〜7日)で、同技術を発表した。

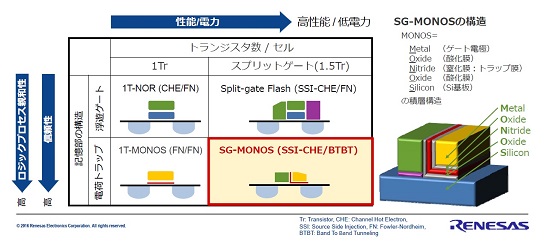

ルネサスは、マイコンに混載するフラッシュメモリ構造として、SG-MONOSを以前から採用してきた。「MONOS」とは、「Metal Oxide Nitride Oxide Silicon」のことで、シリコン基板上に、酸化膜/窒化膜(トラップ膜)/酸化膜の3層を形成し、その上にゲート電極(メタル)を配置する構造である。さらに、ゲート電極を、選択ゲートとメモリゲートの2つに分けている(=Split Gate)ので、「SG-MONOS」という。記憶部の構造としては、チャージトラップ(電荷トラップ)を採用している。

ルネサスはSG-MONOSフラッシュメモリセルを、既に製品化している40nm世代フラッシュ内蔵マイコンなどで使用している。2020年に量産する予定である28nm世代品でも採用する予定だ。

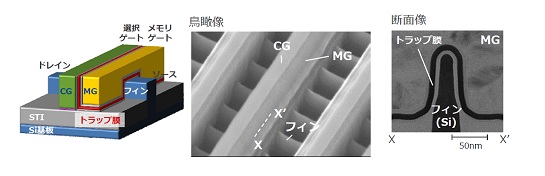

今回ルネサスが発表したメモリセルは、従来のSG-MONOSフラッシュメモリセルに、フィン構造を取り入れたものになる。フィンが形成されたシリコン基板上に、3層の膜とゲート電極を配置したフラッシュメモリセルである。

フィン構造のSG-MONOSフラッシュメモリセル。画像右の「断面像」は、「鳥瞰像」のX/X'で切断した時の断面図となる。フィンの上にトラップ膜が形成されているのがよく分かる(クリックで拡大) 出典:ルネサス

16nm/14nm FinFETの構造に合う不揮発メモリが必要に

先に述べたように、ルネサスは現在、40nm世代のマイコンを量産中で、28nm世代品も開発中である。だが、IoT(モノのインターネット)機器や自動運転車など、さまざまなモノのスマート化が進む中、大量のセンサー情報などを処理するマイコンでは、より大容量、高性能、高信頼性が求められていて、16nm/14nm世代以降へとプロセスを進めていく必要がある。

16nm/14nm世代のロジックICでは、トランジスタにフィン構造を用いる(FinFET)ことで、高性能化や低消費電力化を図っているが、そうなると、フィン構造に適した混載フラッシュメモリが必要になる。複雑な構造を持つFinFETとの親和性が高い混載フラッシュメモリを実現すべく開発したのが、今回のSG-MONOSフラッシュメモリセルになる。

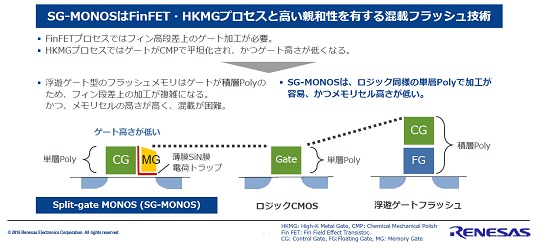

ルネサスの生産本部で技師長を務める塘一仁(つつみ・かずひと)氏は、SG-MONOSフラッシュメモリは、浮遊ゲートフラッシュメモリに比べ、FinFETやHKMG(High-k/Metal Gate)といった先端のロジックプロセスと親和性が高い構造だと説明する。

基板上にフィンを形成し、さらにゲート電極を形成するFinFETプロセスは、段差が多くなるため、ただでさえ高度な加工が必要だ。そこに構造が複雑な浮遊ゲートフラッシュメモリを混載するとなると、段差上で加工することがさらに難しくなる。その点、シンプルな構造を持つSG-MONOSフラッシュメモリは、段差があっても比較的加工しやすい。

HKMGプロセスでは、CMP(Chemical Mechanical Polishing:化学機械研磨)を多用するので、CMOSロジックのゲートが非常に薄くなる(ゲート高さが低くなる)。そのため、浮遊ゲートの上に制御ゲートを積層する浮遊ゲートフラッシュメモリでは、CMOSロジックとの高さの差が大きくなってしまい、混載が難しくなる。その点、制御ゲートの横にメモリゲートが配置されていて、その間に記憶部を設けているSG-MONOSフラッシュメモリは、高さの点で制約が少ないというメリットがある。

Copyright © ITmedia, Inc. All Rights Reserved.