連載

SanDiskが語る、抵抗変化メモリの抵抗値変化:福田昭のストレージ通信(51) 抵抗変化メモリの開発動向(10)(2/2 ページ)

今回は、抵抗変化メモリ(ReRAM)の抵抗値が書き込み後に変化する現象(リラクゼーション)について報告する。十分な書き込み電流を確保すれば抵抗値は安定するが、当然、消費電力は増える。抵抗値の変化を抑えつつ、低い消費電力も実現するにはスイッチング原理の見直しが効果的だ。

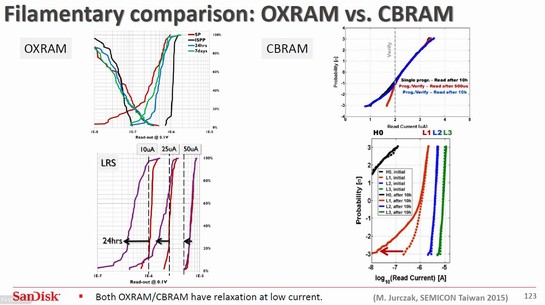

OXRAMとCBRAMは類似の傾向を示す

抵抗変化メモリ(ReRAM)はスイッチング原理の違いにより、OXRAM(Oxide-based RAM)とCBRAM(Conductive Bridge RAM)に大きく分かれる。OXRAMは記憶層に酸化物を採用しており、酸素欠陥あるいは酸素イオンの移動によって抵抗値を制御する。CBRAMは記憶層に絶縁物を採用しており、金属イオンの移動によって絶縁層内に導電性フィラメントを形成することで抵抗値を下げる。

OXRAMとCBRAMのいずれも、書き込み電流が低いと抵抗値の変化が大きい傾向がある。また、メモリセルの特性の違いにも依存する。書き込み直後の読み出し電流が低いメモリセルほど、抵抗値が短時間に上昇する度合いが強い。

スイッチング原理の変更で抵抗値の変化を減らす

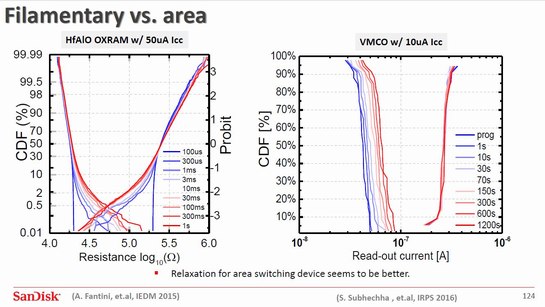

スイッチング原理を見直すことで、小さな抵抗値変化と低い書き込み電流と両立させることは可能だ。例えばimecとルーベン・カトリック大学が共同で開発したVMCO(Vacancy-Modulated Conductive Oxide) RAMは、10μAと低めの書き込み電流で読み出し不良のないメモリセルを実現できている。

スイッチング原理の違いによる、抵抗値変化の違い。左は既出のOXRAM。書き込み電流は50μA。右はVMCO(Vacancy-Modulated Conductive Oxide) RAM。書き込み電流が10μAと低くなっているにもかかわらず、抵抗値の変化が小さい。出典:SanDisk(クリックで拡大)

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

imceによる、5nm世代のロジック配線プロセスを展望した講演を、前後編の2回にわたりお届けする。前半では、配線抵抗(R)、配線容量(C)、RC積という配線のパラメータの特徴を紹介する。さらに、10nm世代、7nm世代、5nm世代と微細化が進むと、配線抵抗(R)、配線容量(C)、RC積がどのように変化していくかを解説する。 求む、「スーパーメモリ」

求む、「スーパーメモリ」

ARM Researchの講演内容を紹介してきたシリーズ。完結編となる今回は、ARMが「スーパーメモリ」と呼ぶ“理想的なメモリ”の仕様を紹介したい。現時点で、このスーパーメモリに最も近いメモリは、どれなのだろうか。 ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス、フィン構造のMONOSフラッシュを開発

ルネサス エレクトロニクスが、フィン構造を採用したSG(Split-Gate型)-MONOSフラッシュメモリセルの開発に成功したと発表した。フィン構造としたことで、FinFETなど先端のロジックプロセスとの親和性が高くなり、次世代の16nm/14nm世代マイコンに混載できるようになる。 新原理のトランジスタによるLSI動作実証に成功

新原理のトランジスタによるLSI動作実証に成功

産業技術総合研究所は2016年12月5日、新原理のトランジスタ「トンネルFET」を用いたLSIの動作実証に成功したことを明らかにした。 2020年、5nm世代でEUV時代が到来か

2020年、5nm世代でEUV時代が到来か

ASMLは2016年4〜6月にEUV(極端紫外線)リソグラフィ装置を4台受注し、2017年には12台を販売する計画を明かした。これを受けて業界では、EUV装置によるチップ量産が、5nmプロセス世代での製造が見込まれる2020年に「始まるかも」との期待感が広がっている。 ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

今回は、コストとパターン形成の2点について、ArF液浸とEUV(極端紫外線)リソグラフィを比べてみよう。ArF液浸では、10nm世代になるとステップ数と重ね合わせ回数が破壊的な数値に達してしまう。これがコストの大幅な上昇を招く。さらに、ArF液浸とEUVでは、10nm世代の配線パターンにも大きな差が出てくる。