製造コスト「数十分の1」、卓上半導体工場:IoTからIoEへ(5/5 ページ)

半導体製造の後工程に革新が生まれそうだ。コネクテックジャパンは製造プロセスを一新することで、後工程に必要なコストを抑え、実装時間を短縮するフリップチップ実装装置「MONSTER DTF」を開発した。特徴は低荷重、低温で半導体パッケージを基板に実装すること。例えばMEMSパッケージをフリップチップ実装できるようになり、最終製品の小型・軽量化にもつながるという。

最終製品の軽量化に役立つ実装技術

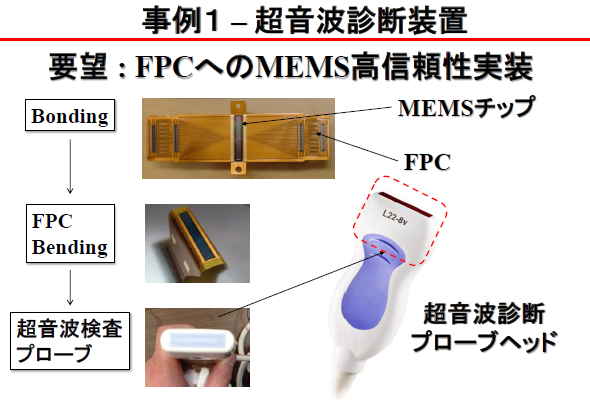

同社のMONSTER PAC技術は、最終製品の小型軽量化にも役立つ。例えば医療用などに用いる超音波診断用のプローブヘッドだ(図9)。

「米スタンフォード大をスピンアウトした企業が開発したMEMSパッケージをMONSTER PAC技術を用いて実装したところ、4〜5kgあった従来製品を200gまで軽量化できた」(平田氏)

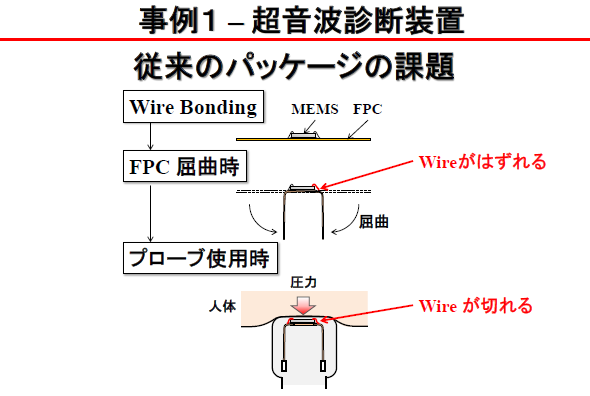

小型軽量化できた理由はこうだ。従来の技術ではフレキシブルプリント回路基板(FPC)に実装後、基板を屈曲させるとワイヤボンディングのワイヤが外れてしまう(図10)。プローブはモノや人に当たるため、実装後に圧力が加わることも多い。このときやはり切れてしまう。同社の技術であれば、フリップチップ実装であるため、このような問題は起きない。

半導体の歩留まり向上を生かす

MONSTER PAC技術を用いた例の中には、半導体チップの歩留まりを高めたことと同じ効果が得られた事例もある。

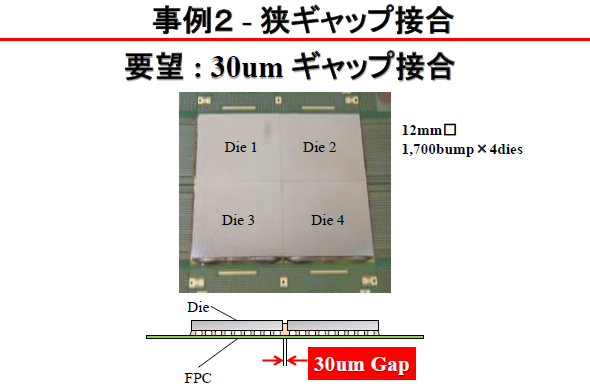

基本的なアイデアはこうだ。ある機能を実現するために、24mm角のASICが必要だとしよう。チップサイズが大きいため、ウエハーに占める面積が大きくなり、ウエハー上の欠陥によって歩留まりは下がる。もしもASICの機能を12mm角4個に分割できれば、ウエハー上の欠陥密度が同じであっても、不良になる比率が下がり、歩留まりは上がる。例えば初期の歩留まりが50%の場合、90%まで向上する。

このような手法が一般的でないのは伝送距離に課題があるからだ。1つのASICを4つに分割すると、チップ間の伝送距離が長くなってしまい、性能が落ちてしまう。

MONSTER PAC技術を用いると、このような設計・実装が可能になる。ある事例では、1700端子あるASICを4つに分割、パッケージ間の距離を30μmに抑えることに成功した(図11)。

従来技術ではフリップチップ実装時にチップに対して100kgfの以上の力を加えていた。これでは充填剤の押し出しが起こり、チップ間の距離が300μm以上に広がってしまう。さらに260℃以上の接合温度に達するため、基板がそる。パッケージ間の距離を短くすることが不可能だった。

低温で接合できるMONSTER PAC技術の特徴を生かすと、大面積のパッケージの下面に別のパッケージを配置するチップオンチップ実装でも、湾曲やパッケージの落下などの問題が起こりにくくなるとした。例えばハイパフォーマンスコンピュータ(HPC)用のCPU基板の実装だ。

従来の手法ではコスト高になったり、そもそも実現できなかった実装が、MONSTER PAC技術と、同技術を使いやすく装置化したMONSTER DTFで可能になりつつある。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

マンションの1室に入る大きさのチップボンダー

マンションの1室に入る大きさのチップボンダー

コネクテックジャパンは、2015年12月16〜18日に東京ビッグサイトで開催された「SEMICON Japan 2015」で、デスクトップ型のフリップチップボンダ―を展示した。 「地図はここに」 40周年SEMICONが魅せる世界

「地図はここに」 40周年SEMICONが魅せる世界

マイクロエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan 2016」(2016年12月14〜16日/東京ビッグサイト)は、2016年の開催で40周年を迎える。主催者であるSEMIジャパンの代表を務める中村修氏に、その見どころなどについて聞いた。 銅配線プロセスとメタルハードマスクで新技術

銅配線プロセスとメタルハードマスクで新技術

アルバックは、「SEMICON Japan 2016」(2016年12月14〜16日/東京ビッグサイト)で、マルチチャンバー型スパッタリング装置として、メインプラットフォーム向け「ENTRON-EX W300」や、小規模量産ライン向け「MLX-3000N」などを紹介する。