製造コスト「数十分の1」、卓上半導体工場:IoTからIoEへ(4/5 ページ)

半導体製造の後工程に革新が生まれそうだ。コネクテックジャパンは製造プロセスを一新することで、後工程に必要なコストを抑え、実装時間を短縮するフリップチップ実装装置「MONSTER DTF」を開発した。特徴は低荷重、低温で半導体パッケージを基板に実装すること。例えばMEMSパッケージをフリップチップ実装できるようになり、最終製品の小型・軽量化にもつながるという。

導電性ペーストとNCPがカギ

MONSTER PAC技術の特徴である低い接合荷重を実現するために、新規材料を開発し、材料を生かした工程を作り上げた。

材料面では2つある。銀を主成分とし、数種類のフィラと混合した導電ペーストが1つ。もう1つは非導電性ペースト(NCP:non conductive paste)だ。

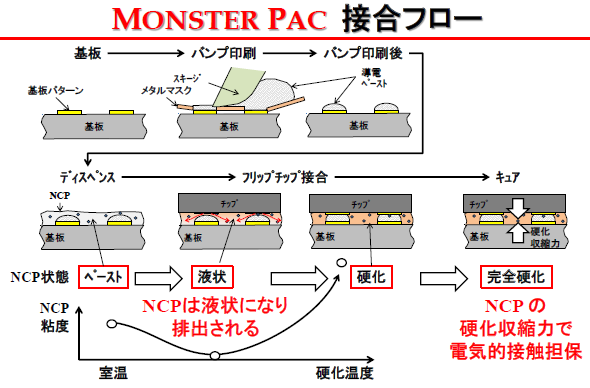

MONSTER DTF装置では、最初の工程で基板上のパターンにスクリーン印刷の一種である凹版印刷を用いて導電ペーストを塗る(図5)。塗り回数は1回だ。この導電ペーストが半導体パッケージとパターンの間の導電路となる。「30μmピッチのバンプを形成でき、現在10μmピッチ対応品を開発中だ」(平田氏)

次の工程では、NCPを注入する。最後に半導体パッケージ(チップ)を載せる。すると、チップ側の端子と導電ペーストが接触する。余分なNCPはパターンの間に排出される。「従来のフリップチップ実装では毛管現象を利用して水のように粘度が低い液体をアンダーフィルとして用いている。当社の手法は全く異なる」(平田氏)

どう異なるのか。NCPが接合に必要な圧力を生み出すことだ。チップを載せた後、雰囲気の温度を高めるとNCPが硬化する。するとNCPが収縮し、チップ端子と導電ペーストが圧着する形で確実に接触する(図6)*3)。

*3) 従来のフリップチップ実装では端子間で金属結合が起こる。MONSTER PAC技術では接触によって導電性を確保する。このため、抵抗が高くなる。「80μmピッチの場合、1端子当たりの抵抗値は20mΩ。はんだと比較すると約10倍だが、実用性を考えれば問題ない値だと考えている」(平田氏)

MEMSパッケージの実装に役立つ

「各種半導体のうち、MEMSパッケージには実装に特に大きな課題がある。現在のスマートフォンですら10個以上のMEMSパッケージを(各種センサーとして)利用している。5G時代になると、SAWフィルターなどもMEMS化していくだろう。つまりMEMSパッケージの搭載数は増える。その一方でMEMSパッケージの実装手法は、実装密度が低いワイヤボンディングだ。最終製品の小型化ができない。矛盾がある。この矛盾を当社の技術であれば解決できる」(平田氏)

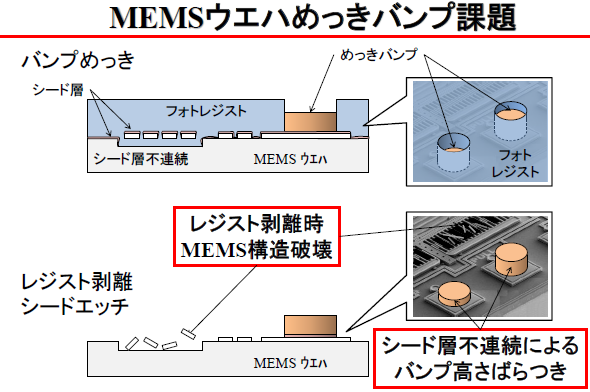

MEMSでフリップチップ実装を試みた場合、課題は大きく2つある。図7にあるようにめっきバンプはフォトレジストで囲まれた筒状の構造になる。さらにMEMSでは特有の段差がある。すると、バンプの高さがばらついてしまう。これでは基板との実装時にうまく接合しない。さらに、フォトレジストを剥離する際にMEMS内にある微細な金属部分が飛んでしまう。

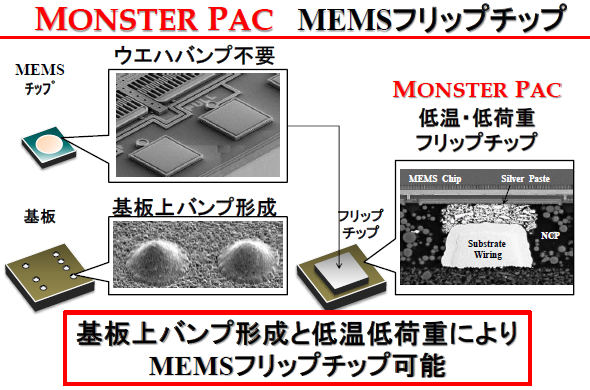

「当社の技術を適用すればウエハー上のバンプがそもそも不要だ(図8)。MEMSの金属構造には触らない。これで課題は解決した。既に国内のメーカーでも当社の技術を採用しており、実装受託開発の引き合いの6割をMEMSのフリップチップ実装が占めているほどだ」(平田氏)

Copyright © ITmedia, Inc. All Rights Reserved.