常時オンの分散プロセッシングを可能にするFPGA:メモリとDSPを増加

ラティスセミコンダクターは、2016年12月12日に発表したモバイル機器市場向けのFPGA「iCE40 UltraPlus」の説明会を開催した。従来品と比較して、多くの機能を新たに追加。常時オン接続で複数のセンサーバッファを、低消費電力で実現することが可能という。

モバイル機器やIoTエッジデバイスに

ラティスセミコンダクターは2016年12月20日、同年12月12日に発表したFPGAの新製品「iCE40 UltraPlus」(以下、UltraPlus)の説明会を開催した。主にモバイル機器市場に向けて、同社が展開してきた「iCE40 Ultra」ファミリー。UltraPlusは、従来シリーズと比較して機能を増やした製品となっている。

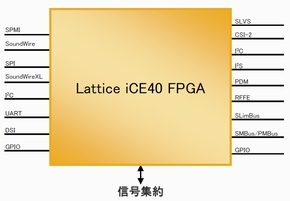

最大5000LUTのロジック領域を持ち、1MビットのRAMを新たに内蔵、DSPを8個に増やした。従来シリーズ「iCE40 Ultra」と比較すると、メモリ容量は8倍、DSP数は2倍である。待機時の消費電流は35μA未満。パッケージサイズ2.15×2.55mmのCSP品(0.4mmピッチ)と、7mm角のQFNパッケージ品(0.5mmピッチ)をそろえた。

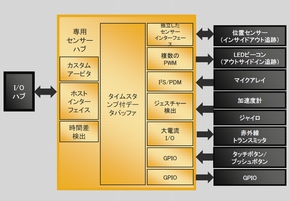

また、I2CやVGIO、SPI、MIPI-DPHYなどのI/Oも新たにサポートした。これにより、モバイル機器やIoTエッジデバイスで求められる、常時オン接続で複数のセンサーバッファを、低消費電力で実現することが可能になるという。

ローカルで演算する「DHP」

同社のアジアパシフィック地域 事業開発担当シニアマネジャーを務める陳英仁氏は、システムアーキテクチャのトレンドについて次のように言及する。スマートフォンやウェアラブル端末などのモバイル機器は、搭載するセンサーからリアルタイムにデータを得られるため、常時オンの状態でいる必要がある。そのときに課題となるのが消費電力だ。

また、1つの機器に搭載するセンサーが増える中、データ処理時間を短くするために高速なI/Oが採用されているため、演算の要求も高まっている。これらの課題に対して、陳氏は「iCE40 UltraPlusは、理想的なソリューション」と語る。

同社はセンサーから得られたデータをクラウドではなく、ローカルで演算するアプローチ「DHP:Distributed Heterogeneous Processing」を進めている。DHPでは、繰り返す数値処理タスクを、エネルギー効率の優れたDSPで実行することで、アプリケーションプロセッサの負荷を低減する。これにより、アプリケーションプロセッサを長時間スリープモードに保ち、システムの消費電力削減するといったアプローチだ。

iCE40 UltraPlusはメモリ容量を8倍、DSPの個数を2倍にしたことで、ローカル処理で低レイテンシで電力効率の高いシステムを開発可能。陳氏は「MCUで良いのではという声もあるかもしれない。しかし、MCUが十分な数のI/Oがなく、複数のセンサーを同時にサンプリングできない。当社のFPGAでは、これらの課題も解決できる」と語る。

評価用サンプルとボードは既に発売済み。価格は、機能を多く追加したため従来シリーズよりは高いが、「モバイル機器向けに対応できる価格」(陳氏)としている。開発環境は「iCEcube2」、製造プロセスはTSMC 40nmプロセスを採用している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Lattice、投資ファンドが13億ドルで買収へ

Lattice、投資ファンドが13億ドルで買収へ

FPGAベンダーであるLattice Semiconductor(ラティス セミコンダクター)が、投資ファンドに買収されることで合意したと発表した。 Xilinx、機械学習の推論に強いFPGAをアピール

Xilinx、機械学習の推論に強いFPGAをアピール

Xilinx(ザイリンクス)は2016年12月、データセンター向けのビジネスに関する記者説明会を都内で開催した。 投資ファンドによるLattice買収に暗雲(前編)

投資ファンドによるLattice買収に暗雲(前編)

2016年11月、米国に拠点を置く未公開株式投資ファンドCanyon Bridge Capital Partnersが、米国のFPGAメーカーLattice Semiconductor(ラティス・セミコンダクター)を13億米ドルで買収すると発表した。だがこれに、米国の規制当局が「待った」をかけている。 インテル、FPGA戦略の踏襲をコミット

インテル、FPGA戦略の踏襲をコミット

Intel(インテル)のグループ会社である日本アルテラは、東京都内で「インテルSoC FPGAデベロッパー・フォーラム(ISDF)」を開催した。SoC FPGAの製品戦略などについて、これまでの方向性を踏襲していくことを表明するとともに、会場では“インテル色”を全面に打ち出した。 NECがCPU-FPGA密結合デバイス用新通信方式を開発

NECがCPU-FPGA密結合デバイス用新通信方式を開発

NECは2016年6月、CPUとFPGAによる密結合プロセッサで、CPUとFPGA間の高速通信を実現するための開発時間を大幅に短縮できる新たなデータ通信方式を開発した。 MIPI D-PHYブリッジIC、ラティスが製品化

MIPI D-PHYブリッジIC、ラティスが製品化

ラティスセミコンダクターは、モバイル機器に搭載されたカメラや表示装置で用いられる主要なプロトコルに対応したMIPI D-PHYブリッジIC「CrossLink」を発表した。