NVIDIAがMOSFETの比例縮小則(デナード則)を解説(前編):福田昭のデバイス通信(97) 高性能コンピューティングの相互接続技術(2)(1/2 ページ)

1970年代から1990年代にかけて、半導体集積回路は「デナード・スケーリング」という法則に沿って高密度化と高速化を達成してきた。今回は、デナード・スケーリングの内容と、なぜ1990年代以降は、この法則に沿って微細化を進めることが困難になったのかを説明する。

デナード・スケーリング(比例縮小則)とは何か

2016年12月に開催された国際学会IEDMのショートコースから、「将来のコンピュータにおける相互接続の課題(Interconnect Challenges for Future Computing)」と題するNVIDIAの講演概要をご紹介している。講演者はNVIDIAで研究担当シニア・バイスプレジデント兼チーフサイエンティストを務めるWilliam(Bill) Dally氏である。

シリーズの初回である前回は、28nm技術のSoC(System on a Chip)シリコンダイを例に、内部バスや入出力リンクなどが消費するエネルギーが、演算器や埋め込みメモリなどが消費するエネルギーよりもはるかに大きいことを明示した。今回は、MOSFETの微細化をけん引してきた「デナード・スケーリング(比例縮小則)」を解説する。

なお講演だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Dally氏の講演内容を適宜、補足している。あらかじめご了承されたい。

「デナード・スケーリング」は「デナード則」あるいは「比例縮小則」「スケーリング則」などとも呼ばれる、MOSFETを微細化するときのメリットを工学的に導出した法則である。1974年にIBMのロバート・デナード(Robert H. Dennard)氏らがIEEEの論文誌で発表した。その概要は、スケーリング係数(k)を基準として、MOSFETのゲート寸法(ゲート長とゲート幅)をk分の1にすると、遅延時間がk分の1に短くなり、消費電力はkの2乗分の1に下がるというもの。つまり、MOSFETは小さくするだけで高速かつ低消費になる、という極めて魅力的な法則である。

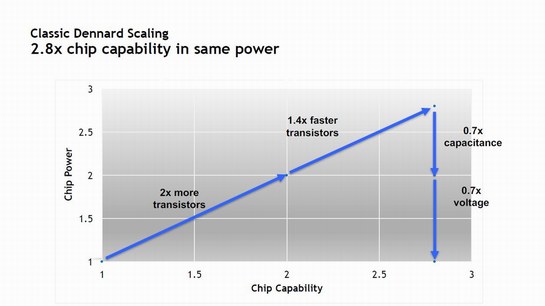

Dally氏の講演では、デナード・スケーリングを以下のように説明した。半導体産業では、「k分の1」が「0.7」になるようにMOSFETの微細化を進めてきた。するとシリコンダイ単位面積当たりのトランジスタ数は2倍になり、トランジスタの速度は1.4倍(kの値そのもの)になる。これだけだとシリコンダイの消費電力が2.8倍に増えてしまう。しかしゲートの静電容量が0.7倍に下がり、電源電圧を0.7倍に下げることで、消費電力はほぼ変わらずに済む。

これが現在では「古典的な(Classic)」と呼ばれて過去のものとなったデナード・スケーリングだ。MOSFETを微細化すると、シリコン面積当たりのトランジスタ数が2倍に増え、速度が1.4倍に高まるにもかかわらず、消費電力が増えない。まるで「魔法のような」法則である。しかも部分的な修正はあったものの、1970年代から1990年代の半導体集積回路はほぼ、デナード・スケーリングに沿って高密度化と高速化を達成してきた。

Copyright © ITmedia, Inc. All Rights Reserved.