3次元集積化(3D IC)の理想と現実:福田昭のデバイス通信(103) TSMCが解説する最先端パッケージング技術(2)(2/2 ページ)

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。

旧世代のパッケージング技術とTSV 3D ICの大きなギャップ

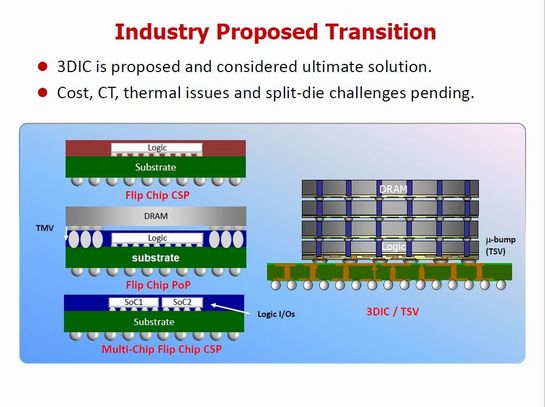

前回で説明したように、複数のチップで構成されたパッケージには、外形寸法を小さくするとともに、動作周波数や帯域幅などを高く維持すること、電力効率を高めること、製造コストを低く維持すること、などが求められる。これらの目標を達成する究極のパッケージング技術として期待されてきたのは、シリコン貫通ビア(TSV: Through Silicon Via)技術によって複数のシリコンダイの積層と接続を実現する3D IC(Three-dimentional Integrated Circuit)だ。

しかし、旧世代のパッケージング技術から見ると、TSV技術による3D ICとの間には大きなギャップが存在した。旧世代のパッケージング技術とは、フリップチップCSP(Chip Scale Package)やフリップチップPoP(Package on Package)、マルチチップのフリップチップCSPなどである。これらのパッケージング技術は、プリント基板と類似の樹脂基板、シリコンダイの表面と樹脂基板をはんだボール経由で接続するフリップチップ技術、樹脂封止技術といった、成熟した安価な要素技術によって構成されていた。

TSV技術による3D ICでは、シリコンダイを貫通する細い孔(ビア)を電極として上下のシリコンダイを微小なバンプ(マイクロバンプ)によって電気的かつ機械的に接続する。TSV技術とマイクロバンプ技術は比較的新しく、製造がそれほど容易ではなく、そして何より、製造コストが高くつく技術である。カネに糸目を付けない一部の特殊な用途を除くと、TSV技術による3D ICへの移行はハードルが高すぎた。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

SanDiskが語る、抵抗変化メモリのセル選択スイッチ技術(前編)

SanDiskが語る、抵抗変化メモリのセル選択スイッチ技術(前編)

抵抗変化メモリ(ReRAM)の記憶容量当たりの製造コストをDRAM以下にするためには、セレクタを2端子のスイッチにする必要がある。2端子セレクタを実現する技術としては、“本命”があるわけではなく、さまざまな技術が研究されている。 Intelが10nmプロセスの詳細を明らかに

Intelが10nmプロセスの詳細を明らかに

Intelは2017年に10nmチップ製造を開始する予定だ。さらに、22nmの低電力FinFET(FinFET low power、以下22nm FFL)プロセスも発表した。GLOBALFOUNDRIESなどが手掛けるFD-SOI(完全空乏型シリコン・オン・インシュレーター)に真っ向から挑み、ファウンドリービジネスで競い合う。 エレクトロニクス産業を動かす“3大潮流”

エレクトロニクス産業を動かす“3大潮流”

変化の激しいエレクトロニクス産業の未来をIHS Markit Technologyのアナリストが予測する。連載第1回は、これからのエレクトロニクス産業を動かしていくであろう“3大潮流”を解説する。 近代科学の創始者たちに、研究不正の疑いあり(コペルニクス編その1)

近代科学の創始者たちに、研究不正の疑いあり(コペルニクス編その1)

1510年ごろ、地動説のひな型となる論文「小論考(コメンタリオルス)」が生まれる。それを書いたのがコペルニクスだ。地動説の端緒となるコペルニクスの偉大さは疑いようもないことだが、その凄さを強調するあまりに現代では、いくつかの誤りが信じられている節がある。 次世代3次元SoCは、TSVを使わない――Qualcomm

次世代3次元SoCは、TSVを使わない――Qualcomm

Qualcommは、米国で開催された「International Symposium on Physical Design(ISPD)」で、同社の3次元SoCの技術動向について語った。TSV(シリコン貫通ビア)を使わずに積層することで、小型化と歩留まりの向上を実現したいという。 シリコンが次の手、村田製作所のキャパシター戦略

シリコンが次の手、村田製作所のキャパシター戦略

2016年10月に村田製作所が買収したフランスのIPDiAは、シリコンキャパシターを事業として手掛けるほぼ唯一のメーカーだ。積層セラミックコンデンサーに比べてかなり高価なシリコンキャパシターは、その用途は限られている。それにもかかわらず、なぜ村田製作所はIPDiAの買収に至ったのか。