福田昭のデバイス通信

私たちの日常に欠かせないものになっているデバイス。それらの進化や課題など、その時々で“気になる話題”を筆者独自の視点で迫る!!

福田昭のデバイス通信(500) EETimes Japan 20周年記念寄稿(その1):

EE Times Japan 創刊20周年に合わせて、半導体業界を長年見てきたジャーナリストの皆さまや、EE Times Japanで記事を執筆していただいている方からの特別寄稿を掲載しています。今回は、40年以上にわたり半導体技術/電子技術を見守り、フリーの技術ジャーナリストとして活躍されている福田昭氏にご寄稿いただきます。EE Times Japan創刊からさらに20年さかのぼり、1985年の話からスタートします。

福田昭のデバイス通信(499) 2024年度版実装技術ロードマップ(19):

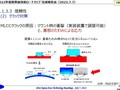

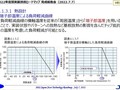

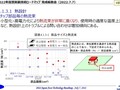

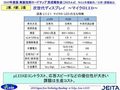

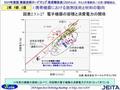

電子情報技術産業協会(JEITA)の「2024年度版 実装技術ロードマップ」(PDF形式電子書籍)を紹介するシリーズ。今回は、「2.4.2 自動運転・遠隔操作」の後半パートとなる「2.4.2.2 要素技術」について説明する。

福田昭のデバイス通信(498) 2024年度版実装技術ロードマップ(18):

今回は、高度道路交通システム(ITS:Intelligent Transport Systems)の無線通信用周波数帯域の再編成について解説する。

福田昭のデバイス通信(497) 2024年度版実装技術ロードマップ(17):

今回は、「協調型自動運転」に関する通信技術を解説する。協調型自動運転を支える通信技術は主に2つある。「V2X(Vehicle-to-Everything)」と「V2N(Vehicle-to-Network)」だ。

福田昭のデバイス通信(496) 2024年度版実装技術ロードマップ(16):

今回は、自動車が搭載する通信技術の動向と自動運転に関連する通信技術を述べる。

福田昭のデバイス通信(495) 2024年度版実装技術ロードマップ(15):

今回はオーナーカー(自家用自動車)とサービスカー(人間あるいは貨物を運ぶ事業に使われる自動車)について、自動運転車両の商品化・商業化状況を説明する。

福田昭のデバイス通信(494) 2024年度版実装技術ロードマップ(14):

今回から「2.4.2 自動運転・遠隔操作」の内容を説明する。この項は、開発動向と要素技術の2つのパートで構成される。

福田昭のデバイス通信(493) 2024年度版実装技術ロードマップ(13):

前回に続き、「第2章第4節(2.4) モビリティー」の第1項、「2.4.1 世界に於けるEVの潮流」の後半部を紹介する。

福田昭のデバイス通信(492) 2024年度版実装技術ロードマップ(12):

今回からは「第2章第4節(2.4) モビリティー」の概要をご報告する。電気自動車(EV)の潮流や自動運転、電動化技術という3つのパートで構成されている。

福田昭のデバイス通信(491) 2024年度版実装技術ロードマップ(11):

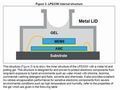

今回は「2.2.2.2 バイオセンサ」の内容から、バイオセンサの組み立て技術をご紹介する。

福田昭のデバイス通信(490) 2024年度版実装技術ロードマップ(10):

今回からは「2.2.2 バイオテクノロジーとデジタルテクノロジーの融合」の概要を紹介する。この項目は、「2.2.2.1 次世代シーケンサと血糖値センサ」「2.2.2.2 バイオセンサ」の2つのパートで構成される。

福田昭のデバイス通信(489) 2024年度版実装技術ロードマップ(9):

「2.2.1.4 ウェアラブルデバイス、ウェアラブル用電源の動向」の後半を紹介する。Appleの「Apple Watch Series 9」、Googleの「Pixel Watch 2」、Samsung Electronicsの「Galaxy Watch 6」を分解し、メイン基板と光電容量脈波センサーの実装状態を観察した。

福田昭のデバイス通信(488) 2024年度版実装技術ロードマップ(8):

今回は「2.2.1.4 ウェアラブルデバイス、ウェアラブル用電源の動向」の概要を紹介する。ウェアラブルデバイスの中でも進化が速い「スマートウォッチ」に注目し、Appleのスマートウォッチ「Apple Watch Series 7/Series 8/Series 9」の仕様を比較している。

福田昭のデバイス通信(487) 2024年度版実装技術ロードマップ(7):

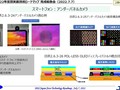

今回は、「2024年度版 実装技術ロードマップ」から、「2.2.1.2 IVD、バイオロジー研究機器:細胞外小胞の網羅的解析機器の事例」の概要を報告する。

福田昭のデバイス通信(486) 2024年度版実装技術ロードマップ(6):

今回は「2.2.1.1 低侵襲性医療:カプセル内視鏡の事例」の後半部分を説明する。カプセル内視鏡の課題や、適用範囲を広げるために必要な改良、次世代のカプセル内視鏡のイメージについて記載されている。

福田昭のデバイス通信(485) 2024年度版実装技術ロードマップ(5):

今回は、第2章第2節第1項(2.2.1)「メディカル・ライフサイエンス市場向けデバイスの事例検討」を紹介する。「2.2.1」の始めは「2.2.1.1 低侵襲性医療:カプセル内視鏡の事例」である。

福田昭のデバイス通信(484) 2024年度版実装技術ロードマップ(4):

今回から「2024年度版 実装技術ロードマップ」の第2章「第2章:注目すべき市場と電子機器群」の内容を紹介していく。

福田昭のデバイス通信(483) 2024年度版実装技術ロードマップ(3):

「2024年度版 実装技術ロードマップ」の「第2章:注目すべき市場と電子機器群」における、前回版との主な違いを紹介する。

福田昭のデバイス通信(482) 2024年度版実装技術ロードマップ(2):

電子情報技術産業協会(JEITA)が2024年6月に発行した「2024年度版 実装技術ロードマップ」の内容を紹介するシリーズ。今回は「第2章:注目すべき市場と電子機器群」を説明する。

福田昭のデバイス通信(481) AIサーバの放熱技術(14):

今回は伝導液冷の優位性を支える最も重要なユニット「CDU(Coolant Distribution Unit)」の仕組みと能力を説明する。

福田昭のデバイス通信(480) AIサーバの放熱技術(13):

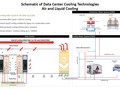

今回は、今後普及するとみられる伝導液冷を解説する。強制空冷に対し、電力コストやインフラ整備の点で優位性がある。

福田昭のデバイス通信(479) AIサーバの放熱技術(12):

今回は、液体冷却技術を紹介する。発熱する部分を冷却プレートによって冷やす「間接・伝導冷却」技術である。

福田昭のデバイス通信(478) AIサーバの放熱技術(11):

今回から、純水や冷却液などの液体を使ってラックマウントサーバを冷却する「液体冷却システム」の概要を解説する。

福田昭のデバイス通信(477) AIサーバの放熱技術(10):

今回は、既存の強制空冷システムに液体冷却ユニットを追加した「ハイブリッド冷却システム」を、さらに強化する手法を説明する。

福田昭のデバイス通信(476) AIサーバの放熱技術(9):

今回は、既存の強制空冷システムに液体冷却システムを追加した「ハイブリッド冷却システム」を解説する。

福田昭のデバイス通信(475) AIサーバの放熱技術(8):

今回は、空冷(空気冷却)技術と液冷(液体冷却)技術の違いを説明する。

福田昭のデバイス通信(474) AIサーバの放熱技術(7):

今回は、「後扉熱交換器(RDHX:Rear Door Heat Exchanger)」方式または「リアドア空調」方式と呼ばれる冷却方式を取り上げる。

福田昭のデバイス通信(473) AIサーバの放熱技術(6):

今回から、データセンターやラックマウントサーバの冷却能力を高める技術を解説する。サーバルーム内に補助となる冷却器を追加する、ラックマウントサーバの排気口で空気を冷やすなどの手法を紹介する。

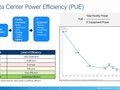

福田昭のデバイス通信(472) AIサーバの放熱技術(5):

AI(人工知能)対応でCPUとGPUの消費電力は増大している。そのため、既存のデータセンターの冷却に大きな負担がかかっている。

福田昭のデバイス通信(471) AIサーバの放熱技術(4):

データセンターの放熱/冷却システムの詳細を解説する。まずは空冷方式を取り上げる。

福田昭のデバイス通信(470) AIサーバの放熱技術(3):

今回は、サーバの主なフォームファクター(外形の形状と寸法)を解説する。大きく分けて、3つのフォームファクターがある。

福田昭のデバイス通信(468) AIサーバの放熱技術(1):

「Hot Chips 2024」の技術講座(チュートリアル)のテーマは放熱技術だった。CPU/GPUの消費電力が増加し、サーバやデータセンターの放熱技術に対する注目が集まっているからだ。本シリーズでは、Hot Chips 2024の技術講座などをベースに、最新の放熱技術を解説する。

福田昭のデバイス通信(467) ECTC現地レポート(5):

「ECTC 2024」は初めて参加者が2000人を突破し、大盛況となった。最終日の昼食会ではラッフル(番号くじ)が行われた。筆者も驚くほど「想定外の豪華賞品」が次々に登場し、会場は大いに盛り上がった。

福田昭のデバイス通信(466)ECTC現地レポート(4):

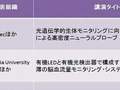

「ECTC 2024」のプレナリーセッションの最終日(2024年5月31日)には、半導体業界の人材育成に関するパネル討論が行われた。その中から中国Central South University(中南大学)と米国Texas Instrumentsの講演を紹介する。

福田昭のデバイス通信(465) ECTC現地レポート(3):

「ECTC 2024」のプレナリーセッションの最終日(2024年5月31日)には、半導体業界の人材育成に関するパネル討論が行われた。その中からいくつかの講演を紹介する。

福田昭のデバイス通信(464) ECTC現地レポート(2):

引き続き、「ECTC 2024」の現地レポートをお届けする。2024年5月30日のプレナリーセッションでは、半導体パッケージングのスタートアップ企業3社が講演を行った。今回は、この3社のプレゼン内容を紹介する。

福田昭のデバイス通信(463) ECTC現地レポート(1):

2024年5月に開催された「ECTC 2024」のレポートを複数回にわたりお届けする。

福田昭のデバイス通信(462) 2024年度版実装技術ロードマップ(1):

電子情報技術産業協会(JEITA)が2年ぶりに実装技術ロードマップを更新し、「2024年度版 実装技術ロードマップ」を2024年6月に発行した。ついに電子書籍となった。2024年6月11日には、5年ぶりとなるリアルでの「完成報告会」を都内で開催した。

福田昭のデバイス通信(461) 2022年度版実装技術ロードマップ(85):

長きにわたり続いてきた「2022年度版実装技術ロードマップ」の解説シリーズは、今回で最終回となる。今回は、基板対基板コネクタと光コネクタの動向を解説する。

福田昭のデバイス通信(460) 2022年度版実装技術ロードマップ(84):

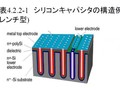

「4.2 基板内蔵部品」のうち、「4.2.2 シリコンキャパシタ」の概要を紹介する。

福田昭のデバイス通信(459) 2022年度版実装技術ロードマップ(83):

今回からは「4.2 基板内蔵部品」の概要を解説する。

福田昭のデバイス通信(458) 2022年度版実装技術ロードマップ(82):

今回は、「4.1.3.4 実装」の後半2つの項目である「適切なはんだ量の設定」と「スルーホールリフロー(THR)対応コンデンサ」について解説する。

福田昭のデバイス通信(457) 2022年度版実装技術ロードマップ(81):

今回は、「4.1.3 部品実装・設計時の注意点」の4番目の項目である「4.1.3.4 実装」を取り上げる。実装の不良の要因と対策を説明する。

福田昭のデバイス通信(456) 2022年度版実装技術ロードマップ(80):

「4.1.3.3 信頼性」の概要を説明する。前回の「振動対策」と「クラック対策」に続き、今回は「電蝕対策」の内容を解説する。

福田昭のデバイス通信(455) 2022年度版実装技術ロードマップ(79):

今回は「4.1.3.3 信頼性」の概要を説明する。その中から、「振動対策」と「クラック対策」を取り上げる。

福田昭のデバイス通信(454) 2022年度版実装技術ロードマップ(78):

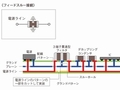

今回は「(2)3端子貫通型フィルタの接続と実装のポイント」の概要を説明する。3端子貫通型フィルタを電源ラインに接続する2つの方法と、それぞれの用途を解説する。

福田昭のデバイス通信(453) 2022年度版実装技術ロードマップ(77):

今回から、第4章第1節第3項「4.1.3 部品実装・設計時の注意点」の2番目の項目、「4.1.3.2 電気性能」の概要を説明する。

福田昭のデバイス通信(452) 2022年度版実装技術ロードマップ(76):

後編となる今回は、「チップ抵抗器の温度上昇と基板放熱の関係」と、「基板放熱に適した新たな温度基準と取組み」の概要を紹介する。

福田昭のデバイス通信(451) 2022年度版実装技術ロードマップ(75):

今回から、第4章第1節第3項「部品実装・設計時の注意点」の概要を説明していく。この項は、「熱設計」「電気性能」などの4つのパートで構成される。

福田昭のデバイス通信(450) 2022年度版実装技術ロードマップ(74):

後編となる今回は、「セラミックコンデンサの高容量化・低ESR化、薄型化」や「チップ抵抗器の高電力化」について解説する。

福田昭のデバイス通信(449) 2022年度版実装技術ロードマップ(73):

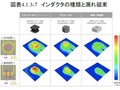

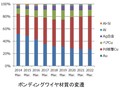

前回に続き、第4章「電子部品」の概要を説明する。「4.1.2 技術動向」は、「インダクタのインダクタンス値の拡大」など、3つの項目で構成される。

福田昭のデバイス通信(448) 2022年度版実装技術ロードマップ(72):

JEITA「2022年度版 実装技術ロードマップ」を解説するシリーズ。今回から、第4章「電子部品」の概要を説明していく。

福田昭のデバイス通信(447) 2022年度版実装技術ロードマップ(71):

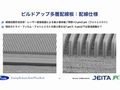

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。

福田昭のデバイス通信(446) 2022年度版実装技術ロードマップ(70):

JEITA「2022年度版 実装技術ロードマップ」の「パッケージ組立プロセス技術動向」について解説するシリーズ。今回は第3章第4節第6項(3.4.6)「電磁シールド」の概要を説明する。

福田昭のデバイス通信(445) 2022年度版実装技術ロードマップ(69):

今回は第3章第4節第5項(3.4.5)「樹脂封止技術(アンダーフィル、モールディング)」の概要を説明する。

福田昭のデバイス通信(444) 2022年度版実装技術ロードマップ(68):

今回は、第3章第4節第4項(3.4.4)「ダイボンディングおよび電極ボンディング技術」の概要を説明する。

福田昭のデバイス通信(443) 2022年度版実装技術ロードマップ(67):

今回は第3章第4節第3項(3.4.3)「ウエハ(チップ)薄型化技術とウエハハンドリング」の概要を説明する。第3項は、裏面研磨技術、ウエハーダイシング技術、DBG(Dicing Before Grinding)プロセスの3つで構成される。

福田昭のデバイス通信(442) 2022年度版実装技術ロードマップ(66):

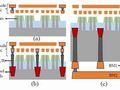

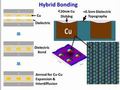

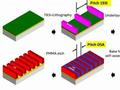

今回から、第3章第4節(3.4)「パッケージ組立プロセス技術動向」の内容を紹介する。本稿では、ハイブリッドボンディングを解説する。

福田昭のデバイス通信(441) 2022年度版実装技術ロードマップ(65):

今回は、第3章第3節第10項(3.3.10)「その他の表面実装パッケージ」の概要を説明する。

福田昭のデバイス通信(440) 2022年度版実装技術ロードマップ(64):

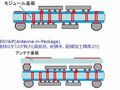

後編となる今回は、誘電体材料パターニング方法とAiP(Antenna in Package)の概要を紹介する。

福田昭のデバイス通信(439) 2022年度版実装技術ロードマップ(63):

今回は第3章第3節第5項(3.3.5)「RFデバイスのパッケージ構造と高速・高周波向け配線材料」の概要を紹介する。

福田昭のデバイス通信(438) 2022年度版実装技術ロードマップ(62):

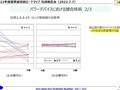

今回は、第3章第3節第4項「車載パワーデバイス」から、「パワーデバイスの発展」を解説する。

福田昭のデバイス通信(437) 2022年度版実装技術ロードマップ(61):

今回は、FO-WLP(Fan Out-Wafer Level Package)のロードマップと、FO-PLP(Fan Out-Panel Level Package)の一種ともみなせる部品内蔵基板について解説する。

福田昭のデバイス通信(436) 2022年度版実装技術ロードマップ(60):

今回は初期の「FO-WLP」で生じた信頼性の問題と、問題を解決した組み立てプロセス、再配線層(RDL)を微細化したプロセスを解説する。

福田昭のデバイス通信(435) 2022年度版実装技術ロードマップ(59):

引き続き、各種パッケージ技術の動向を紹介する第3章第3節を取り上げる。今回から「3.3.2.2 FO-WLP、FO-PLP、部品内蔵基板」の概要を紹介する。

福田昭のデバイス通信(434) 2022年度版実装技術ロードマップ(58):

今回は第3章第3節第2項(3.3.2)「ウェハレベルパッケージ(WLP)、パネルレベルパッケージ(PLP)、部品内蔵基板」の概要をご説明する。

福田昭のデバイス通信(433) 2022年度版実装技術ロードマップ(57):

前回に続き、第3章「電子デバイスパッケージ」の概要を説明する。今回から、第3章第3節(3.3)「各種パッケージ技術動向」の概要を報告する。

福田昭のデバイス通信(432) 2022年度版実装技術ロードマップ(56):

今回からは、「2022年度版 実装技術ロードマップ」の第3章「電子デバイスパッケージ」の概要説明に入る。

福田昭のデバイス通信(431) 2022年度版実装技術ロードマップ(55):

今回は、「パワーデバイスにおける接合材料の現状と課題」の概要を紹介する。

福田昭のデバイス通信(430) 2022年度版実装技術ロードマップ(54):

今回は、第2章第6節第6項「2.6.6 接合材料」から、「SMT(Surface Mount Technology)における接合材料の現状と課題」の概要を紹介する。

福田昭のデバイス通信(429) 2022年度版実装技術ロードマップ(53):

JEITAが発行する「2022年度版 実装技術ロードマップ」を紹介するシリーズ。今回から、第2章第6節第6項「2.6.6 接合材料」の概要を紹介していく。

福田昭のデバイス通信(428) 2022年度版実装技術ロードマップ(52):

今回は「2.6.5.2 量子コンピュータ」と「2.6.5.3 量子計測・センシング」の概要を紹介する。

福田昭のデバイス通信(427) 2022年度版実装技術ロードマップ(51):

今回は、第2章第6節第5項「2.6.5 量子技術」の内容を簡単に説明する。

福田昭のデバイス通信(426) 2022年度版実装技術ロードマップ(50):

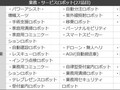

今回は、第2章第6節第4項「ロボット」の概要を解説する。

福田昭のデバイス通信(425) 2022年度版実装技術ロードマップ(49):

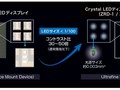

今回は、タブレット/スマートフォン/ノートPC向けディスプレイの概要を説明する。

福田昭のデバイス通信(424) 2022年度版実装技術ロードマップ(48):

前編に続き、テレビ(TV)用ディスプレイの概要を紹介する。今回は、有機ELディスプレイパネル、ローカルディミング用BLU LCDパネル、デュアルセル型LCDパネルを取り上げる。

福田昭のデバイス通信(423) 2022年度版実装技術ロードマップ(47):

今回から、テレビ(TV)用ディスプレイの概要を紹介する。本稿では、TV用ディスプレイの市場予測と、ディスプレイ駆動TFTの種類を取り上げる。

福田昭のデバイス通信(422) 2022年度版実装技術ロードマップ(46):

後編となる今回は、最も小さなディスプレイ用LEDである「マイクロLED(micro LED)」とそのディスプレイを紹介する。

福田昭のデバイス通信(421) 2022年度版実装技術ロードマップ(45):

今回は発光ダイオード(LED)を画素とする超大型ディスプレイ(超大型スクリーン)の概要を紹介する。

福田昭のデバイス通信(420) 2022年度版実装技術ロードマップ(44):

今回から、第2章第6節「新技術・新材料・新市場」の2番目のテーマである「次世代ディスプレイデバイス」について解説する。

福田昭のデバイス通信(419) 2022年度版実装技術ロードマップ(43):

今回は、化石燃料を使わない発電技術の動向を簡単に解説する。

福田昭のデバイス通信(418) 2022年度版実装技術ロードマップ(42):

今回から、第2章第6節(2.6)「新技術・新材料・新市場」の概要を紹介していく。この節では、エレクトロニクス産業で注目を集めているテーマを取り上げる。

福田昭のデバイス通信(417) 2022年度版実装技術ロードマップ(41):

今回はモビリティーの電動化で複雑性が増す「EMC・ノイズ対策」の概要を紹介する。

福田昭のデバイス通信(416) 2022年度版実装技術ロードマップ(40):

今回は「電動化技術」の第6パート「2.5.3.6 航空機と空飛ぶクルマ」の内容を紹介する。

福田昭のデバイス通信(415) 2022年度版実装技術ロードマップ(39):

今回は、電気自動車(EV)の充電インフラでも設計思想が全く異なる、バッテリ交換式システムをご紹介する。

福田昭のデバイス通信(414) 2022年度版実装技術ロードマップ(38):

前編に続き、電気自動車(EV)の充電インフラの動向を説明する。後編では充電方式について解説する。

福田昭のデバイス通信(413) 2022年度版実装技術ロードマップ(37):

今回は、電気自動車の道路走行を支える充電インフラ(充電ステーション)の動向を説明する。

福田昭のデバイス通信(412) 2022年度版実装技術ロードマップ(36):

今回は、電気自動車(BEV:Battery Electric Vehicle)に不可欠の電子ユニットである「インバーター」について解説する。

福田昭のデバイス通信(411) 2022年度版実装技術ロードマップ(35):

今回は、第2章第5節の第3項(2.5.3)「電動化技術」から、「機電一体化」の概要を取り上げる。機電一体化とは何か、メリットとデメリットは何かを説明する。

福田昭のデバイス通信(410) 2022年度版実装技術ロードマップ(34):

前回に続き、第2章第5節の第3項(2.5.3)「電動化技術」の概要を紹介する。その中から、世界における自動車の環境規制動向に相当する部分を解説する。

福田昭のデバイス通信(409) 2022年度版実装技術ロードマップ(33):

今回は第2章第5節の第3項(2.5.3)「電動化技術」の概要を紹介する。第3項は、6つのテーマで構成されている。

福田昭のデバイス通信(408) 2022年度版実装技術ロードマップ(32):

第2章第5節(2.5)「モビリティー」から、第2項(2.5.2)「自動運転と遠隔操作」の内容を抜粋して紹介する。自動運転技術に向けたコンソーシアムや、センシング技術を取り上げる。

福田昭のデバイス通信(407) 2022年度版実装技術ロードマップ(31):

第2章第5節(2.5)「モビリティー」の概要を説明するシリーズ。今回は「自動運転と遠隔操作」の内容を説明する。

福田昭のデバイス通信(406) 2022年度版実装技術ロードマップ(30):

今回からは第2章第5節(2.5)「モビリティー」の概要を説明する。第5節は、「自動運転・遠隔操作」「電動化技術」を含む5つの項目から構成されている。

福田昭のデバイス通信(405) 2022年度版実装技術ロードマップ(29):

前編に続き、「6G」を実現するために必要な要素技術を解説する。仮想化端末、メタサーフェス反射板、通信衛星などの技術を簡単に紹介していく。

福田昭のデバイス通信(404) 2022年度版実装技術ロードマップ(28):

今回から、「6G」を実現するために必要な要素技術を解説する。

福田昭のデバイス通信(403) 2022年度版実装技術ロードマップ(27):

今回は、インターネットと並ぶ情報通信の基幹技術「移動体通信システム」の動向を取り上げる。

福田昭のデバイス通信(402) 2022年度版実装技術ロードマップ(26):

今回から、「2022年度版 実装技術ロードマップ」の第2章第4節である「情報通信」の概要を紹介する。第4節は「情報通信概要」「データセンターサーバー」「モバイル」の3項で構成されている。

福田昭のデバイス通信(401) 2022年度版実装技術ロードマップ(25):

今回は、ヒトの嗅覚に近い機能を備えるセンシングシステム「人工電子鼻(e-Nose:Electronic Nose)」の概要をご説明する。

福田昭のデバイス通信(400) 2022年度版実装技術ロードマップ(24):

前回に続き、「におい」を定量的に評価する手法を取り上げる。今回は「成分濃度表示法(機器分析法)」を紹介する。

福田昭のデバイス通信(399) 2022年度版実装技術ロードマップ(23):

今回は、複雑で抽象的な存在である「におい」を定量的に評価する手法を取り上げる。

福田昭のデバイス通信(398) 2022年度版実装技術ロードマップ(22):

今回から「嗅覚」の概要をシリーズで取り上げる。本稿では、「におい」を感じる意味とその複雑さについて解説する。

福田昭のデバイス通信(397) 2022年度版実装技術ロードマップ(21):

「味覚」の概要を取り上げるシリーズの続き。本稿では、味覚を定量的に検出する「味覚センサー」とその意義について解説する。

福田昭のデバイス通信(396) 2022年度版実装技術ロードマップ(20):

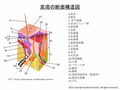

前回に続き、「味覚」の概要を取り上げる。舌の表面構造と味蕾の構造、味蕾が味を感じる仕組みを解説する。

福田昭のデバイス通信(395) 2022年度版実装技術ロードマップ(19):

今回は、第3項(2.3.3)「人間拡張」から6つ目の項目である「味覚」の概要を説明する。

福田昭のデバイス通信(394) 2022年度版実装技術ロードマップ(18):

前回に続き、「触覚」について解説する。今回取り上げるのは、触覚をセンシングするデバイス、「触覚センサー」だ。

福田昭のデバイス通信(393) 2022年度版実装技術ロードマップ(17):

前回に続き、第3項(2.3.3)「人間拡張」の概要を説明する。今回と次回で、「触覚」について解説する。

福田昭のデバイス通信(392) 2022年度版実装技術ロードマップ(16):

JEITAの「2022年度版 実装ロードマップ」を紹介するシリーズ。今回から、第3項(2.3.3)「人間拡張」の概要を説明する。

福田昭のデバイス通信(391) 2022年度版実装技術ロードマップ(15):

前編に続き、バイオセンサの信号検出原理を解説する。具体的には、電気化学インピーダンス測定、イオン感応型FET、グラフェンFET、表面増強ラマン散乱などを取り上げる。

福田昭のデバイス通信(390) 2022年度版実装技術ロードマップ(14):

前回に続き、第2項(2.3.2)「メディカル」の最後の項目、「バイオセンサ」を取り上げる。バイオセンサの主な信号検出原理を説明する。

福田昭のデバイス通信(389) 2022年度版実装技術ロードマップ(13):

今回は、第2項(2.3.2)「メディカル」の最後の項目、「バイオセンサ」を取り上げる。

福田昭のデバイス通信(388) 2022年度版実装技術ロードマップ(12):

「ウイルス性感染症とPCR検査、遺伝子検査」の後半部分を簡単に説明する。

福田昭のデバイス通信(387) 2022年度版実装技術ロードマップ(11):

今回と次回は、JEITAの「2022年度版 実装ロードマップ」から、「感染症とPCR検査、遺伝子検査、迅速検査」(2.3.2.3)の概要をご紹介する。

福田昭のデバイス通信(386) 2022年度版実装技術ロードマップ(10):

JEITAの「2022年度版 実装ロードマップ」を紹介するシリーズ。今回は、第2章「注目される市場と電子機器群」から「マイクロ流体デバイス」の概要を簡単にご紹介する。

福田昭のデバイス通信(385) 2022年度版実装技術ロードマップ(9):

今回は、「(5)医療診断におけるAI活用状況」部分の概要を説明する。

福田昭のデバイス通信(384) 2022年度版実装技術ロードマップ(8):

今回は、「(4)医療分野における5G活用状況」部分の概要を解説する。

福田昭のデバイス通信(383) 2022年度版実装技術ロードマップ(7):

今回は、「手術支援ロボット」(2.3.2.1)から「(2)手術支援ロボットの動向」部分の概要を取り上げる。国産初の手術支援ロボット「hinotori」について説明する。

福田昭のデバイス通信(382) 2022年度版実装技術ロードマップ(6):

今回からは第2項(2.3.2)「メディカル」の概要を報告していく。「メディカル」は「手術支援ロボット」(2.3.2.1)、「マイクロ流体デバイス」(2.3.2.2)、「感染症とPCR検査、遺伝子検査、迅速検査」(2.3.2.3)、「バイオセンサ」(2.3.2.4)の4つの項目で構成される。

福田昭のデバイス通信(381) 2022年度版実装技術ロードマップ(5):

今回は第2章第3節第1項(2.3.1)「ヘルスケアデバイス」の概要をご報告する。

福田昭のデバイス通信(380) 2022年度版実装技術ロードマップ(4):

今回から、第2章「注目される市場と電子機器群」の本論に入る。はじめは第3節(2.3)「ヒューマンサイエンス」の概要を説明する。

福田昭のデバイス通信(379) 2022年度版実装技術ロードマップ(3):

今回は「2022年度版 実装ロードマップ」から、第2節(2.2)「電子機器群の分類と定義」の概要をご紹介する。

福田昭のデバイス通信(378) 2022年度版実装技術ロードマップ(2):

今回から、「2022年度版 実装ロードマップ」の第2章「注目される市場と電子機器群」の概要を複数回に分けて説明していく。

福田昭のデバイス通信(377) 2022年度版実装技術ロードマップ(1):

今回から「2022年度版 実装技術ロードマップ」の概要を連載シリーズでご報告する。

福田昭のデバイス通信(376):

今回は、CXL(Compute Express Link)インタフェースを通じてメモリを拡張する仕組みを説明する。

福田昭のデバイス通信(375):

今回は、第4世代EPYCプロセッサのメモリ構成を簡単にご報告する。具体的には、メインメモリ(主記憶)を解説する。

福田昭のデバイス通信(374):

今回は「Zen4」コアを内蔵するダイ(CCD:Core Complex Die)のメモリ構成をご紹介する。

福田昭のデバイス通信(373):

今回は、Zenアーキテクチャのx86互換64ビットCPUコアで第4世代となる「Zen4」の概要をご紹介する。

福田昭のデバイス通信(372):

今回は、AMDの「第4世代EPYC」と「EPYC 9004シリーズ」の開発と技術仕様に関する情報を紹介する。具体的には開発ロードマップやプロセッサの内部ブロック、マルチプロセッサ構成などを説明する。

福田昭のデバイス通信(371):

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。

福田昭のデバイス通信(370) imecが語るワイヤレス電力伝送技術(24):

今回は、本シリーズの完結回として「8. 将来への展望」の講演部分を紹介する。

福田昭のデバイス通信(369) imecが語るワイヤレス電力伝送技術(23):

今回は「7.4 試作例」の講演パートを解説する。ワイヤレス受電端末を試作し、低消費電力の小型機器をワイヤレス電力伝送で動かした。

福田昭のデバイス通信(368) imecが語るワイヤレス電力伝送技術(22):

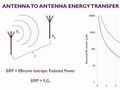

今回は「7.2 アンテナ」と「7.3 アンテナの集積化」の内容について、簡単に解説する。

福田昭のデバイス通信(367) imecが語るワイヤレス電力伝送技術(21):

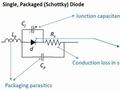

今回から、「7. 放射型ワイヤレス電力伝送の応用例」の講演部分を紹介する。主に受信側の回路を解説する。

福田昭のデバイス通信(366) imecが語るワイヤレス電力伝送技術(20):

今回は、レクテナの後段に位置する直流コンバータ(昇圧と降圧)について解説する。

福田昭のデバイス通信(365) imecが語るワイヤレス電力伝送技術(19):

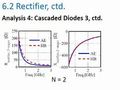

ダイオードを使った整流回路の解析について、複数のダイオードを接続した整流回路兼電圧逓倍回路を解説する。

福田昭のデバイス通信(364) imecが語るワイヤレス電力伝送技術(18):

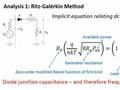

今回は、常微分方程式を数値計算によって解く手法と、EDAソフトウェアを活用する手法を紹介する。

福田昭のデバイス通信(363) imecが語るワイヤレス電力伝送技術(17):

今回は近似解を求める手法である「Ritz-Galerkin(リッツ・ガラーキン)法」を簡単に説明しよう。

福田昭のデバイス通信(362) imecが語るワイヤレス電力伝送技術(16):

今回からは、「6.2 整流器(Rectifier)」に関する講演のサブパートを解説する。

福田昭のデバイス通信(361) imecが語るワイヤレス電力伝送技術(15):

前編に続き、「レクテナ」の要素部品であるアンテナを解説する。後編となる今回は、小型アンテナの代表的な事例と、特性の計算手法を紹介していく。

福田昭のデバイス通信(360) imecが語るワイヤレス電力伝送技術(14):

今回は、「6.1 アンテナ」の講演部分を紹介する。

福田昭のデバイス通信(359) imecが語るワイヤレス電力伝送技術(13):

今回からは、レクテナに関する講演部分を解説する。

福田昭のデバイス通信(358) imecが語るワイヤレス電力伝送技術(12):

今回は4番目のサブパート「5.4 利用可能な周波数帯域と許容電力レベル」と、5番目のサブパート「5.5 結論」の講演部分を説明していく。

福田昭のデバイス通信(357) imecが語るワイヤレス電力伝送技術(11):

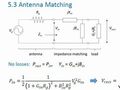

今回は「5.3 アンテナの整合」の講演部分を説明する。

福田昭のデバイス通信(356) imecが語るワイヤレス電力伝送技術(10):

今回は、「フリスの伝達公式」について解説する。

福田昭のデバイス通信(355) imecが語るワイヤレス電力伝送技術(9):

今回は、アンテナ(主に送電用アンテナ)を解説した講演部分を紹介する。

福田昭のデバイス通信(354) imecが語るワイヤレス電力伝送技術(8):

今回からは、マイクロ波を使った電力伝送の基礎理論に関する講演部分を紹介していく。理論的な支えとなる学問は「電磁気学」と「アンテナ工学」である。

福田昭のデバイス通信(353) imecが語るワイヤレス電力伝送技術(7):

後編では、ウイリアム・ブラウン(William C. Brown、1916年5月22日生〜1999年2月3日没)による実験の概要を説明する。

福田昭のデバイス通信(352) imecが語るワイヤレス電力伝送技術(6):

今回からは、電磁波を使った電力伝送をさらに発展させた実験と構想を前後編で紹介していく。

福田昭のデバイス通信(351) imecが語るワイヤレス電力伝送技術(5):

後編では、電磁波の発見によって信号伝送(無線通信)と電力伝送が考案され、試みられていった歴史を簡単に説明する。

福田昭のデバイス通信(350) imecが語るワイヤレス電力伝送技術(4):

今回からはワイヤレス電力伝送の歴史を振り返る。

福田昭のデバイス通信(349) imecが語るワイヤレス電力伝送技術(3):

後編となる今回は、誘導型(非放射型)ワイヤレス電力伝送(WPT)の簡略史と、放射型WPT技術の種類を解説する。

福田昭のデバイス通信(348) imecが語るワイヤレス電力伝送技術(2):

前回に続き、「IEDM 2021」の講演を紹介する。今回から、ワイヤレス電力伝送の基本原理を前後編に分けて解説する。

福田昭のデバイス通信(347) imecが語るワイヤレス電力伝送技術(1):

今回から、「IEDM 2021」でオランダimec Holst Centreでシニアリサーチャー、オランダEindhoven University of TechnologyでフルプロフェッサーをつとめるHubregt J. Visser氏が講演した「Practical Implementation of Wireless Power Transfer(ワイヤレス電力伝送の実用的な実装)」の内容を紹介する。

福田昭のデバイス通信(346) TSMCが開発してきた最先端パッケージング技術(19):

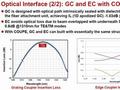

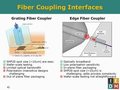

今回は、シリコン光導波路と光ファイバを「COUPE」が高い効率で結合可能であることを示す。

福田昭のデバイス通信(345) TSMCが開発してきた最先端パッケージング技術(18):

前回に続き、TSMCが考えるPE(Photonic Engine)の実現方法「COUPE(COmpact Universal Photonic Engine)」を紹介する。今回は、「COUPE」の電気的な性能をシミュレーションした結果をご報告する。

福田昭のデバイス通信(344) TSMCが開発してきた最先端パッケージング技術(17):

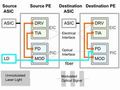

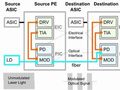

今回は電気信号を光信号に変換(あるいは電気信号を光信号に変換)する回路ユニット「フォトニックエンジン(PE:Photonic Engine)」の構成と、TSMCが考えるPEの実現手法「COUPE(COmpact Universal Photonic Engine)」の概念を説明する。

福田昭のデバイス通信(343) TSMCが開発してきた最先端パッケージング技術(16):

今回から、「シリコンフォトニクス」に関する講演部分を紹介していく。

福田昭のデバイス通信(342) TSMCが開発してきた最先端パッケージング技術(15):

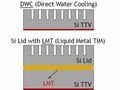

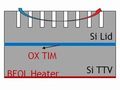

今回は、3種類の放熱構造で冷却性能を比較した結果を紹介する。

福田昭のデバイス通信(341) TSMCが開発してきた最先端パッケージング技術(14):

前回に続き、放熱技術について解説する。TSMCは同技術を「ISMC(Integrated Si Micro-Cooler)」と呼ぶ。

福田昭のデバイス通信(340) TSMCが開発してきた最先端パッケージング技術(13):

今回からは、異種のデバイスを集積化する技術に関する講演部分を説明していく。まずは、放熱技術について解説する。

福田昭のデバイス通信(339) TSMCが開発してきた最先端パッケージング技術(12):

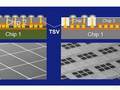

今回は、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」の開発ロードマップを紹介する。

福田昭のデバイス通信(338) TSMCが開発してきた最先端パッケージング技術(11):

今回から、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」を解説する。

福田昭のデバイス通信(337) TSMCが開発してきた最先端パッケージング技術(10):

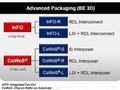

今回からは「CoWoS」の派生品である「CoWoS_R(RDL Interposer)」と「CoWoS_L(Local Silicon Interconnect + RDL Interposer)」の概要を解説する。

福田昭のデバイス通信(336) TSMCが開発してきた最先端パッケージング技術(9):

今回は「CoWoS」の標準仕様について解説する。【訂正あり】

福田昭のデバイス通信(335) TSMCが開発してきた最先端パッケージング技術(8):

前編に続き、「CoWoS(Chip on Wafer on Substrate、コワース)」の進化について解説する。

福田昭のデバイス通信(334) TSMCが開発してきた最先端パッケージング技術(7):

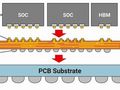

今回からは、高性能コンピューティング(HPC)向けパッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」を解説する。

福田昭のデバイス通信(333) TSMCが開発してきた最先端パッケージング技術(6):

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。

福田昭のデバイス通信(332) TSMCが開発してきた最先端パッケージング技術(5):

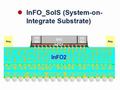

今回から、さらに高い性能のコンピューティングに向けて「InFO」技術を改良した2種類のパッケージを解説する。

福田昭のデバイス通信(331) TSMCが開発してきた最先端パッケージング技術(4):

今回はInFOを高性能コンピューティング(HPC)向けに改良した「InFO_oS(InFO-on-Substrate)」を説明する。

福田昭のデバイス通信(330) TSMCが開発してきた最先端パッケージング技術(3):

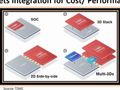

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。

福田昭のデバイス通信(329) TSMCが開発してきた最先端パッケージング技術(2):

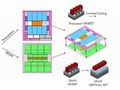

今回は、フロントエンド3Dとバックエンド3Dを解説する他、TSMCが「CSYS(Complementary Systems, SoCs and Chiplets integration、シーシス)」と呼ぶソリューションを紹介する。

福田昭のデバイス通信(328) TSMCが開発してきた最先端パッケージング技術(1):

今回から、2021年8月にオンラインで開催された「Hot Chips」の技術講座より、「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」の講演内容を紹介する。

福田昭のデバイス通信(327) imecが語る3nm以降のCMOS技術(30):

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。

福田昭のデバイス通信(326) imecが語る3nm以降のCMOS技術(29):

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。

福田昭のデバイス通信(325) imecが語る3nm以降のCMOS技術(28):

今回から、「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演概要を説明する。

福田昭のデバイス通信(324) imecが語る3nm以降のCMOS技術(27):

後編となる今回は、1本のスーパービアがブロックするトラック数を減らしたときに生じる問題と、その解決策を述べる。

福田昭のデバイス通信(323) imecが語る3nm以降のCMOS技術(26):

今回から、スーパービアが抱える本質的な課題と、その解決策を前後編の2回に分けて解説する。

福田昭のデバイス通信(322) imecが語る3nm以降のCMOS技術(25):

今回は、奇数番号(あるいは偶数番号)で隣接する配線層(2層上あるいは2層下の配線層)を接続するビア電極の抵抗を大幅に下げる技術、「スーパービア(supervia)」について解説する。

福田昭のデバイス通信(321) imecが語る3nm以降のCMOS技術(24):

今回は、多層配線技術の中核を成すビア電極技術について解説する。

福田昭のデバイス通信(320) imecが語る3nm以降のCMOS技術(23):

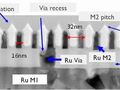

今回は、銅配線からルテニウム配線への移行と微細化ロードマップについて紹介する。

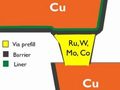

福田昭のデバイス通信(319) imecが語る3nm以降のCMOS技術(22):

前回から「次世代の多層配線(BEOL)技術」の講演内容を紹介している。今回は、銅(Cu)以外の配線技術を導入する際の候補となる高融点金属について解説する。

福田昭のデバイス通信(318) imecが語る3nm以降のCMOS技術(21):

「IEDM2020」の講演内容を紹介するシリーズ。今回から、「次世代の多層配線(BEOL)技術」の講演内容を紹介していく。

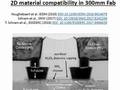

福田昭のデバイス通信(317) imecが語る3nm以降のCMOS技術(20):

今回は、2次元材料の特長と、集積回路の実現に向けた課題について紹介する。

福田昭のデバイス通信(316) imecが語る3nm以降のCMOS技術(19):

「IEDM2020」の講演内容を紹介するシリーズ。今回から、「さらにその先を担うトランジスタ技術(ポストシリコン材料)」の講演部分を解説する。

福田昭のデバイス通信(315) imecが語る3nm以降のCMOS技術(18):

後編となる今回は、「シーケンシャル(Sequential)CFET」の具体的な試作例を紹介する。

福田昭のデバイス通信(314) imecが語る3nm以降のCMOS技術(17):

今回と次回は「シーケンシャル(Sequential)CFET」の重要な特徴である、ボトム側とトップ側で異なるトランジスタ材料が選べることの利点と、実際にCFETを試作した事例を解説する。

福田昭のデバイス通信(313) imecが語る3nm以降のCMOS技術(16):

今回は前回に続いてシーケンシャルCFETの講演部分を説明する。モノリシックCFETに比べるとシーケンシャルCFETの製造プロセスは難しくない。ただし製造プロセスには大きな制約が付きまとう。前回はその1つである、ウエハーを貼り合わせる界面で欠陥が発生する問題と対策を述べた。今回はもう1つの課題である、温度条件を解説しよう。

福田昭のデバイス通信(312) imecが語る3nm以降のCMOS技術(15):

今回は、下側(底側、ボトム側)のトランジスタを作り込んでから、その上に別のウエハーを貼り合わせて上側(頂側、トップ側)のトランジスタを作成する「シーケンシャル(Sequential)CFET」の製造プロセスを解説する。

福田昭のデバイス通信(311) imecが語る3nm以降のCMOS技術(14):

今回から、2種類のCFETの製造プロセスを解説していく。始めは「モノリシックCFET」を取り上げる。

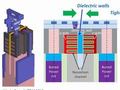

福田昭のデバイス通信(310) imecが語る3nm以降のCMOS技術(13):

今回はCFETのトランジスタ構造と、CFETは製造方法の違いによって2種類に分けられることを説明する。

福田昭のデバイス通信(309) imecが語る3nm以降のCMOS技術(12):

引き続き、FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET/CFET)の講演部分を紹介する。今回は、CFETがCMOS基本セルの微細化に与えるメリットを具体的に解説する。

福田昭のデバイス通信(308) imecが語る3nm以降のCMOS技術(11):

今回から、「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を解説する。

福田昭のデバイス通信(307) imecが語る3nm以降のCMOS技術(10):

今回は基本的な論理回路セルとSRAMセルで、FinFETとナノシート構造、フォークシート構造のシリコン面積がどのくらい変化するかを説明する。

福田昭のデバイス通信(306) imecが語る3nm以降のCMOS技術(9):

今回は、フォークシート構造のCMOSロジックを製造するプロセスを解説するとともに、試作したトランジスタの断面を電子顕微鏡と蛍光X線分析で観察した画像を提示する。

福田昭のデバイス通信(305) imecが語る3nm以降のCMOS技術(8):

今回は、CMOSロジックの基本セル(スタンダードセル)を微細化する手法の変化と、フォークシート構造の利点について解説する。

福田昭のデバイス通信(304) imecが語る3nm以降のCMOS技術(7):

前回に続き、「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を紹介する。imecは、フォークシート構造のトランジスタの研究開発に力を入れている。

福田昭のデバイス通信(303) imecが語る3nm以降のCMOS技術(6):

今回からは「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を報告していく。

福田昭のデバイス通信(302) imecが語る3nm以降のCMOS技術(5):

今回は、CMOSロジックの基本セル(スタンダードセル)に電源を分配する電源供給配線網(PDN:Power Delivery Network)のレイアウトを解説する。

福田昭のデバイス通信(301) imecが語る3nm以降のCMOS技術(4):

今回は、BPR(Buried Power Rail)の複雑な構造を説明する略語を定義するとともに、金属材料の候補を解説する。

福田昭のデバイス通信(300) imecが語る3nm以降のCMOS技術(3):

電源/接地配線を基板側に埋め込む「BPR(Buried Power Rails)」について解説する。

福田昭のデバイス通信(299) imecが語る3nm以降のCMOS技術(2):

今回は、CMOSロジックの高密度化手法を簡単に解説する。

福田昭のデバイス通信(298) imecが語る3nm以降のCMOS技術(1):

「IEDM2020」から、imecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏の講演内容を紹介する。CMOSを3nm以下に微細化するための要素技術を解説する講演だ。

福田昭のデバイス通信(297) Intelが語るオンチップの多層配線技術(18):

本シリーズの最終回となる今回は、シングルダイ(1枚のシリコンダイ)にモノリシックに成長させる3次元集積化技術について解説する。

福田昭のデバイス通信(296) Intelが語るオンチップの多層配線技術(17):

今回は、異種デバイスの融合を実現する3次元(3D)集積化技術の概要を説明する。

福田昭のデバイス通信(295) Intelが語るオンチップの多層配線技術(16):

今回は、自己組織化単分子(SAM)膜を使った選択成長の工程を説明する。

福田昭のデバイス通信(294) Intelが語るオンチップの多層配線技術(15):

今回から、基板表面の一部だけを選んで薄膜を堆積(成長)させる技術(「選択デポジション(selective deposition)」あるいは「選択成長(selective growth)」)と、選択成長技術がビアの位置ずれ不良に応用できることを説明する。

福田昭のデバイス通信(293) Intelが語るオンチップの多層配線技術(14):

今回は、自己組織化リソグラフィがEUV(極端紫外線)リソグラフィの弱点を補完する技術であることを説明する。

福田昭のデバイス通信(292) Intelが語るオンチップの多層配線技術(13):

前回に続き、「自己組織化リソグラフィ(DSAリソグラフィ)」について解説する。

福田昭のデバイス通信(291) Intelが語るオンチップの多層配線技術(12):

今回から、ArF液浸技術やEUV(極端紫外線)技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術「自己組織化リソグラフィ」をご紹介する。

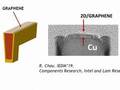

福田昭のデバイス通信(290) Intelが語るオンチップの多層配線技術(11):

今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」について解説する。

福田昭のデバイス通信(289) Intelが語るオンチップの多層配線技術(10):

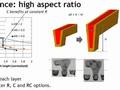

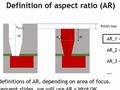

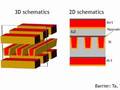

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。

福田昭のデバイス通信(288) Intelが語るオンチップの多層配線技術(9):

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。

福田昭のデバイス通信(287) Intelが語るオンチップの多層配線技術(8):

今回は、金属配線の抵抗と容量を大きく左右する、配線の「アスペクト比(AR:Aspect Ratio)」について解説する。

福田昭のデバイス通信(286) Intelが語るオンチップの多層配線技術(7):

前回に続き、配線プロセスの代表であるダマシン技術とサブトラクティブ技術を解説する。

福田昭のデバイス通信(285) Intelが語るオンチップの多層配線技術(6):

今回は、配線製造プロセスの基本部分である、配線パターンの形成技術「ダマシン(damascene)技術」と「サブトラクティブ(subtractive)技術」にについて解説する。

福田昭のデバイス通信(284) Intelが語るオンチップの多層配線技術(5):

今回から、多層配線の微細化と性能向上を両立させる要素技術について解説していく。

福田昭のデバイス通信(283) Intelが語るオンチップの多層配線技術(4):

今回は、銅(Cu)配線の寸法と静電容量(単位長当たりの容量値)の関係を説明する。

福田昭のデバイス通信(282) Intelが語るオンチップの多層配線技術(3):

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。

福田昭のデバイス通信(281) Intelが語るオンチップの多層配線技術(2):

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。

福田昭のデバイス通信(280) Intelが語るオンチップの多層配線技術(1):

2020年6月にオンラインで開催された「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介する。

福田昭のデバイス通信(279) 2019年度版実装技術ロードマップ(87):

「2019年度版実装技術ロードマップ」解説の最終回となる今回は、前回に続き実装設備間の次世代通信規格「SEMI SMT-ELS」について説明する。

福田昭のデバイス通信(278) 2019年度版実装技術ロードマップ(86):

実装ラインの次世代通信規格を前後編で解説する。前編となる今回は、従来の通信規格「SMEMA」と、それを置き換える「JARAS1014」を紹介する。

福田昭のデバイス通信(277) 2019年度版実装技術ロードマップ(85):

今回は、実装設備の将来像と今後の課題を取り上げる。

福田昭のデバイス通信(276) 2019年度版実装技術ロードマップ(84):

今回は「封止材料」に対するユーザーの要望を調査した結果を紹介する。

福田昭のデバイス通信(275) 2019年度版実装技術ロードマップ(83):

ロードマップ第6章「実装設備」の第4節「実装技術動向」を説明するシリーズ。今回は、「接合材料」に対するユーザーの要望を調査した結果を紹介する。

福田昭のデバイス通信(274) 2019年度版実装技術ロードマップ(82):

引き続き、「実装技術動向」を紹介する。今回は、実装設備が対応すべき、プリント配線板と部品供給方式のロードマップについて解説する。

福田昭のデバイス通信(273) 2019年度版実装技術ロードマップ(81):

今回から、第6章「実装設備」の第4節「実装技術動向」を説明する。まずはチップ部品の技術ロードマップを取り上げる。

福田昭のデバイス通信(272) 2019年度版実装技術ロードマップ(80):

実装設備に要求する項目のアンケート結果を紹介するシリーズ。今回は「ベアチップ/フリップチップボンダ」に対する要求を説明する。

福田昭のデバイス通信(271) 2019年度版実装技術ロードマップ(79):

引き続き、実装設備に要求する項目のアンケート結果を紹介する。今回は、「検査機」に対する要求と対策を取り上げる。

福田昭のデバイス通信(270) 2019年度版実装技術ロードマップ(78):

前回に続き、実装設備に要求する項目のアンケート結果を紹介する。今回は「リフロー(リフローはんだ付け装置)」に対する要求と対策を説明する。

福田昭のデバイス通信(269) 2019年度版実装技術ロードマップ(77):

引き続きアンケート結果を紹介する。今回は「マウンタに対する要求と動向」についてで、実装設備の中では最も多い回答件数を集めている。

福田昭のデバイス通信(268) 2019年度版実装技術ロードマップ(76):

今回から、実装設備に対する具体的な要求項目の重要度(順位)を説明していく。まずは「印刷機(スクリーン印刷機)」を取り上げたい。

福田昭のデバイス通信(267) 2019年度版実装技術ロードマップ(75):

今回から、実装設備のユーザー(セットメーカーやモジュールメーカー、アセンブリ受託企業など)が実装設備に要求する項目と重要度を、JEITAがアンケート調査した結果を報告していく。

福田昭のデバイス通信(266) 2019年度版実装技術ロードマップ(74):

今回は実装工程の生産性を左右する2つの要因を解説する。1つは実装設備(主にマウンタ)の速度、もう1つはマウンタにおける部品の補充や段取り換えなどに要する時間である。

福田昭のデバイス通信(265) 2019年度版実装技術ロードマップ(73):

第6章「実装設備」の概要を説明する。まずは表面実装の設備と材料を取り上げる。

福田昭のデバイス通信(264) 2019年度版実装技術ロードマップ(72):

今回は「有機樹脂基板(有機樹脂サブストレート)」と「ガラス基板(ガラスサブストレート)」、「パネルレベル基板(パネルレベルサブストレート)」の技術ロードマップを紹介する。

福田昭のデバイス通信(263) 2019年度版実装技術ロードマップ(71):

今回から、第3節「プリント配線板技術ロードマップ」の概要をお届けする。まずは「半導体パッケージ基板(サブストレート)」のロードマップを紹介する。

福田昭のデバイス通信(262) 2019年度版実装技術ロードマップ(70):

今回は、異なる製造技術によって付加価値を高める技術「ストレッチャブル配線板」「コンフォーマブルエレクトロニクス」「テキスタイルエレクトロニクス」の3つを取り上げる。

福田昭のデバイス通信(261) 2019年度版実装技術ロードマップ(69):

今回は、新世代のプリント配線板を代表する「機能集積基板」の概要を解説する。半導体チップや受動部品などを内蔵することで複数の機能を持たせた基板である。

福田昭のデバイス通信(260) 2019年度版実装技術ロードマップ(68):

プリント配線板では多種多様な絶縁基材が使われる。新世代のプリント配線板が採用した新しい絶縁基材について解説する。

福田昭のデバイス通信(259) 2019年度版実装技術ロードマップ(67):

今回から、従来型のプリント配線板と、付加価値を高めた新しいプリント配線板について解説する。

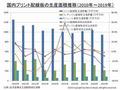

福田昭のデバイス通信(258) 2019年度版実装技術ロードマップ(66):

この10年減少傾向が続いている国内のプリント配線板では、知識集約型の新しいアーキテクチャによる、付加価値の高いプリント配線板が望まれている。

福田昭のデバイス通信(257) 2019年度版実装技術ロードマップ(65):

今回は、「2019年度版 実装技術ロードマップ」の第5章「プリント配線板」の原典である「2019年度版 プリント配線板技術ロードマップ」の概要を紹介する。

福田昭のデバイス通信(256) 2019年度版実装技術ロードマップ(64):

今回から、第5章「プリント配線板」の概要を解説していく。まずは伝統的なプリント配線板の用語と製造方法を紹介しよう。

福田昭のデバイス通信(255) 2019年度版実装技術ロードマップ(63):

今回は、運転操作の品質を低下させないように、あるいは品質を向上させるように工夫した車載用HMIデバイスの一つとして「ステアリング・スイッチ」を紹介する。

福田昭のデバイス通信(254) 2019年度版実装技術ロードマップ(62):

今回から、車載用のHMI(Human Machine Interface)デバイスを紹介する。昔の自動車に比べ、現在の自動車には、運転操作とは直接関係のない車載用HMIデバイスの搭載が増えている。

福田昭のデバイス通信(253) 2019年度版実装技術ロードマップ(61):

今回はタッチパネルの機能、技術動向を解説する。主に、「大型化」「曲面化」「低反射技術」「表面カバーパネル」技術、「メタルメッシュセンサー(金属メッシュ電極)」技術という5つの方向と課題がある。

福田昭のデバイス通信(252) 2019年度版実装技術ロードマップ(60):

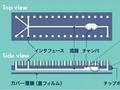

今回は、タッチパネルの構造を解説する。タッチパネルの構造は「外付け型」と「内蔵型」に大別される。

福田昭のデバイス通信(251) 2019年度版実装技術ロードマップ(59):

今回は、「入出力デバイス」からタッチパネルを取り上げる。タッチセンサーについて、主要な5つの方式を紹介する。

福田昭のデバイス通信(250) 2019年度版実装技術ロードマップ(58):

今回はToF(Time of Flight)デバイスの概要と市場、技術動向を説明する。

福田昭のデバイス通信(249) 2019年度版実装技術ロードマップ(57):

今回から「入出力デバイス」の概要を紹介する。入出力デバイスとして取り上げるものは、ToFセンサー、タッチパネル、車載用HMIデバイスである。

福田昭のデバイス通信(248):

前回に続き、京都セミコンダクターが発表した赤外線フォトダイオード(PD)「KPMC29(KP-2 Two-tone PD)」について解説する。今回は、同製品の特長と構造を説明したい。

福田昭のデバイス通信(247):

京都セミコンダクターが、受光波長範囲が広く、高さが1.1mmと薄型の赤外線フォトダイオード(PD)を製品化した。同製品を、PDの解説と併せて紹介する。

福田昭のデバイス通信(246) 2019年度版実装技術ロードマップ(56):

今回は、車載セーフティ用コネクタ(車載カメラ用コネクタを含む)の10年後に関し、コネクタメーカーに対してアンケート調査を実施した結果を説明する。10社が回答した。

福田昭のデバイス通信(245) 2019年度版実装技術ロードマップ(55):

今回は自動車用カメラと、そのコネクタについて説明する。

福田昭のデバイス通信(244) 2019年度版実装技術ロードマップ(54):

今回は自動車用のコネクタを解説する。車載用コネクタは「パワートレイン(駆動系)用」「セーフティ(安全系)用」「インフォテインメント(情報・通信系)用」「ボディ系用」の4つに大別される。

福田昭のデバイス通信(243) 2019年度版実装技術ロードマップ(53):

今回からコネクタを紹介する。まずはコネクタの種類と用途について解説する。

福田昭のデバイス通信(242) 2019年度版実装技術ロードマップ(52):

今回は超音波センサーを取り上げる。超音波センサーの原理と種類を説明する。

福田昭のデバイス通信(241) 2019年度版実装技術ロードマップ(51):

MEMSセンサーを前後編で紹介している。後編となる今回は、圧力センサーと傾斜センサーについて解説する。

福田昭のデバイス通信(240) 2019年度版実装技術ロードマップ(50):

代表的なMEMSセンサーとその用途を前後編で説明する。今回は加速度センサーとジャイロセンサーについて解説する。

福田昭のデバイス通信(239) 2019年度版実装技術ロードマップ(49):

今回は、自動運転を支えるMEMSセンサーと、その応用について解説する。

福田昭のデバイス通信(238) 2019年度版実装技術ロードマップ(48):

自動車用センサーの後編では、超音波センサー、LiDAR、内装(インテリア)用センサーを取り上げ、それぞれの仕組みと用途を紹介する。

福田昭のデバイス通信(237) 2019年度版実装技術ロードマップ(47):

今回から、自動車におけるセンサーの技術動向を前後編に分けて紹介する。前編では、対象物をリアルタイムで認識するカメラと、定速走行・車間距離制御を支えるミリ波レーダーについて解説する。

福田昭のデバイス通信(236) 2019年度版実装技術ロードマップ(46):

今回からMEMSセンサーを解説する。MEMSセンサーの市場規模と主なアプリケーションについて説明したい。

福田昭のデバイス通信(235) 2019年度版実装技術ロードマップ(45):

「2019年度版 実装技術ロードマップ」を紹介するシリーズ。今回から、センサーを説明する。多種多様なセンサーの種類と、センサー市場を解説する。

福田昭のデバイス通信(234) 2019年度版実装技術ロードマップ(44):

今回は、ESD対策に特化した電子部品「ESDサプレッサ」の概要を解説する。バリスタとの違いや、主な仕様を取り上げる。

福田昭のデバイス通信(233) 2019年度版実装技術ロードマップ(43):

今回から、EMC対策部品のうち、電子回路を雷サージや静電気放電(ESD)などの雑音から保護する部品を説明する。まずは「積層チップバリスタ」について解説する。

福田昭のデバイス通信(232) 2019年度版実装技術ロードマップ(42):

前回に続き、コモンモードフィルタ(CMF:Common Mode Filter)について説明する。今回は、コモンモードフィルタの種類と特性パラメータ、最近の製品動向を解説する。

福田昭のデバイス通信(231) 2019年度版実装技術ロードマップ(41):

今回は、チップビーズとともにEMC対策部品の代表ともいえる「コモンモードフィルタ」の概要を説明する。

福田昭のデバイス通信(230) 2019年度版実装技術ロードマップ(40):

「2019年度版 実装技術ロードマップ」を紹介するシリーズ。前回から「4.2 EMC対策部品」の概要を解説している。今回は、代表的なEMC対策部品の1つである「チップビーズ」を解説する。

福田昭のデバイス通信(229) 2019年度版実装技術ロードマップ(39):

「2019年度版 実装技術ロードマップ」を紹介するシリーズ。今回から、「4.2 EMC対策部品」の概要を解説していく。まずは、EMC規制の始まりやEMC対策の考え方、EMC対策部品の主な機能について解説する。

福田昭のデバイス通信(228) 2019年度版実装技術ロードマップ(38):

今回は、表面実装型抵抗器の主流である「チップ抵抗器」を取り上げる。チップ抵抗器の進化の方向性は大きく「小型化」「高放熱化」「耐硫化」の3つがある。それぞれについて解説する。

福田昭のデバイス通信(227) 2019年度版実装技術ロードマップ(37):

今回は、次世代のコンデンサである「シリコンキャパシタ(シリコンコンデンサ)」を解説する。

福田昭のデバイス通信(226) 2019年度版実装技術ロードマップ(36):

今回は、大容量で低コストという特長を持つアルミ電解コンデンサを解説する。アルミ電解コンデンサの分類と、車載および無線分野におけるアルミ電解コンデンサの要件を紹介しよう。

福田昭のデバイス通信(225) 2019年度版実装技術ロードマップ(35):

今回はフィルムコンデンサを解説する。フィルムコンデンサの特性は、誘電体として使われるプラスチック材料によってかなり異なる。代表的な4つの材料を紹介しよう。

福田昭のデバイス通信(224) 2019年度版実装技術ロードマップ(34):

今回は、積層セラミックコンデンサ(MLCC)を取り上げる。積層セラミックコンデンサの特長と、小型化、大容量化の推移をたどる。

福田昭のデバイス通信(223) 2019年度版実装技術ロードマップ(33):

第4章「電子部品」からコンデンサについて解説する。コンデンサの構造や働き、種類を説明しよう。

福田昭のデバイス通信(222) 2019年度版実装技術ロードマップ(32):

今回は、第4章「電子部品」からインダクタについて説明する。インダクタの構造の他、電源用インダクタの用途と特性を紹介する。

福田昭のデバイス通信(221) 2019年度版実装技術ロードマップ(31):

「2019年度版 実装技術ロードマップ」を紹介するシリーズ。今回から、第4章「電子部品」を取り上げる。まずは、インダクタ、コンデンサ、抵抗器の更新内容をお伝えする。

福田昭のデバイス通信(220):

2019年12月に開催された「IEDM 2019」の記者室に、国際学会VLSIシンポジウムの実行委員会が“乱入”し、シンポジウムの開催概要を説明した。今回は、そのミニ説明会の内容を紹介する。

福田昭のデバイス通信(219) 2019年度版実装技術ロードマップ(30):

今回は、部品内蔵基板の組み立て工程を紹介する。半導体チップをフェースダウン(回路面を下にした状態)で基板に搭載する技術、フェースアップ(回路面を上にした状態)で基板に搭載する技術、微細な配線を形成できる技術の3つについて解説したい。

福田昭のデバイス通信(218) 2019年度版実装技術ロードマップ(29):

前回に続き、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。今回は、微細配線を形成可能なFO-WLPを取り上げる。

福田昭のデバイス通信(217) 2019年度版実装技術ロードマップ(28):

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。

福田昭のデバイス通信(216) 2019年度版実装技術ロードマップ(27):

今回から、パッケージの組み立てプロセスの技術動向を紹介する。まずは、QFN、BGA、WL-CSP、FO-WLPの組み立て工程を取り上げる。

福田昭のデバイス通信(215) 2019年度版実装技術ロードマップ(26):

今回は、第5世代(5G)の移動通信システムに向けたミリ波対応のSiP(System in Package)技術を紹介する。ミリ波帯向けでは、アンテナとFEM(Front End Module)を積層した「AiP(Antenna in Package)というSiPの実用化が始まっている。

福田昭のデバイス通信(214) 2019年度版実装技術ロードマップ(25):

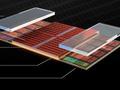

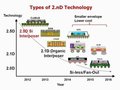

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。

福田昭のデバイス通信(213) 2019年度版実装技術ロードマップ(24):

今回は第3章「電子デバイスパッケージ」から、各種パッケージの技術動向を紹介する。半導体パッケージの歴史は、多端子化と小型化、薄型化、低コスト化の歴史でもある。

福田昭のデバイス通信(212) 2019年度版実装技術ロードマップ(23):

今回から、第3章「電子デバイスパッケージ」の概要を説明していく。「2019年度版 実装技術ロードマップ」で約70ページが割かれている重要な章だ。序章では、年間で1兆個のセンサーが生産される「トリリオンセンサー」について言及している。【訂正あり】

福田昭のデバイス通信(211) 2019年度版実装技術ロードマップ(22):

前回に続き、「第5世代(5G)移動通信システム」の内容を紹介するシリーズ。今回は、4G(第4世代)から5Gへの移行シナリオについて説明する。

福田昭のデバイス通信(210) 2019年度版実装技術ロードマップ(21):

「第5世代(5G)移動通信システム」の内容を紹介するシリーズ。今回は、5Gで利用する3つの周波数帯と、移動体通信事業者4社の割り当てについて説明する。

福田昭のデバイス通信(209) 2019年度版実装技術ロードマップ(20):

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」の概要をシリーズで伝えている。今回から「第5世代(5G)移動通信システム」の内容を説明していく。

福田昭のデバイス通信(208) 2019年度版実装技術ロードマップ(19):

マイクロLEDディスプレイパネルの関連特許出願動向や各メーカーの研究開発動向を紹介していく。

福田昭のデバイス通信(207) 2019年度版実装技術ロードマップ(18):

今回は、次世代フラットパネルディスプレイのキーデバイスを解説する「2.5.2 マイクロLED」を取り上げる。マイクロLEDパネルの強みとは何だろうか。

福田昭のデバイス通信(206) 2019年度版実装技術ロードマップ(17):

今回は、ロードマップ第2章第5節「サーマルマネジメント」から、「携帯機器における放熱技術と材料の動向」の概要を取り上げる。

福田昭のデバイス通信(205) 2019年度版実装技術ロードマップ(16):

今回は、ロードマップ第2章第5節の最初の項目である「サーマルマネジメント」から、「パワーモジュールにおける放熱技術と材料の動向」の概要を解説していく。

福田昭のデバイス通信(204) 2019年度版実装技術ロードマップ(15):

今回から、ロードマップ第2章第5節「新技術・新材料・新市場」を取り上げる。まずは、5節の最初の項目である「サーマルマネジメント」から紹介していこう。

福田昭のデバイス通信(203) 2019年度版実装技術ロードマップ(14):

今回は、電動化のキーデバイスである「パワーデバイス」に関してロードマップが記述した部分の概要をご紹介していく。

福田昭のデバイス通信(202) 2019年度版実装技術ロードマップ(13):

今回も、「モビリティー」から、「2.4.4 電動化」の概要を紹介する。今回は鉄道車両と航空機の電動化に関する部分の概要を取り上げる。

福田昭のデバイス通信(201) 2019年度版実装技術ロードマップ(12):

今回から、ロードマップの「モビリティー」のうち「電動化」について紹介していく。まずはハイブリッド自動車と電気自動車、燃料電池自動車の違いと、電動化した自動車の構成要素を取り上げよう。

福田昭のデバイス通信(200) 2019年度版実装技術ロードマップ(11):

ロードマップ第2章「注目される市場と電子機器群」から、3番目の大テーマである「モビリティー」の概要を説明している。今回は、前回に引き続き「コネクティッド化」に関する部分について紹介する。

福田昭のデバイス通信(199) 2019年度版実装技術ロードマップ(10):

ロードマップ第2章「注目される市場と電子機器群」から、3番目の大テーマである「モビリティー」の概要を説明している。今回は「コネクティッド化」に関する部分の概要を説明する。

福田昭のデバイス通信(198) 2019年度版実装技術ロードマップ(9):

前回に続き、ロードマップ第2章「注目される市場と電子機器群」から、3番目の大テーマである「モビリティー」の概要を説明する。今回は、特に「レベル3」の自動運転を提供するECU(電子制御ユニット)と、それに搭載される半導体チップに焦点を当てたい。

福田昭のデバイス通信(197) 2019年度版実装技術ロードマップ(8):

今回から、第2章「注目される市場と電子機器群」で3番目の大テーマとなる「モビリティー」を紹介していく。2019年版のロードマップでは、「自動運転化」「コネクティッド化」「電動化」という3つのワードが含まれていることが、2015年版や2017年版とは大きく異なる点だ。

福田昭のデバイス通信(196) 2019年度版実装技術ロードマップ(7):

今回は、「メディカル・ライフサイエンス(医療・生命科学)」から後半部分の概要を報告する。特に、2017年度版ロードマップの読者アンケートで関心が高かった「バイオセンサー」に焦点を当てる。

福田昭のデバイス通信(195) 2019年度版実装技術ロードマップ(6):

今回は、「メディカル・ライフサイエンス(医療・生命科学)」から前半部分の概要を報告する。同分野でのエレクトロニクス技術に対するニーズや、エレクトロニクス技術が貢献できそうな事柄には、どんなものがあるのだろうか。

福田昭のデバイス通信(194) 2019年度版実装技術ロードマップ(5):

前回に続き、第2章のテーマ「情報通信」の後半部分を紹介する。今回のキーワードは、LPWA(Low Power Wide Area)無線ネットワークと、現実空間と仮想空間を融合させるクロスリアリティーだ。

福田昭のデバイス通信(193) 2019年度版実装技術ロードマップ(4):

今回は、第2章の大テーマの一つである「情報通信」の前半部分を紹介する。ここでキーワードとなるのが「Society 5.0」だ。

福田昭のデバイス通信(192) 2019年度版実装技術ロードマップ(3):

JEITAが発行した「2019年度版 実装技術ロードマップ」について、「注目される市場と電子機器群」の分類と定義を紹介する。2019年度版では、大テーマが「情報通信」「メディカル・ライフサイエンス(医療・生命科学)」「モビリティー」「新技術・新材料・新市場」となっている。

福田昭のデバイス通信(191) 2019年度版実装技術ロードマップ(2):

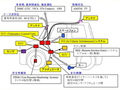

JEITAが発行した「2019年度版 実装技術ロードマップ」に関する完成報告会から、概要を説明するシリーズ。ロードマップ作成で中心的な役割を果たしたJisso技術ロードマップ専門委員会の5つのミッションと、2019年度版ロードマップで注目すべき4点を紹介する。

福田昭のデバイス通信(190) 2019年度版実装技術ロードマップ(1):

今回から、JEITAが作成した「2019年度版 実装技術ロードマップ」の概要を紹介していく。まずは、2019年6月4日に開催された同書の完成報告会のプログラムと、ロードマップ本体の目次を見てみよう。【訂正あり】

福田昭のデバイス通信(189) Intelの「始まり」を振り返る(22):

Intelの創業10年目となる1977年。今回はマイクロコンピュータ製品の動向を説明する。

福田昭のデバイス通信(188)Intelの「始まり」を振り返る(21):

Intelにとって創業10年目である1977年の状況を紹介している。前回は1977年の主な出来事をご説明した。今回は、1977年における半導体製品の状況を解説する。

福田昭のデバイス通信(187) Intelの「始まり」を振り返る(20):

Intelにとって創業10年目である1977年の状況を紹介している。前回は1977年の業績概要をご説明した。今回は1977年の主な出来事を報告する。

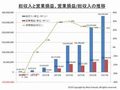

福田昭のデバイス通信(186) Intelの「始まり」を振り返る(19):

Intelの創業10年目(1977年)に焦点を当てる。この年の売上高は前年比25%増の2億8255万米ドル。前年(1976年)に続き、過去最高の収入と利益を更新した。

福田昭のデバイス通信(185) Intelの「始まり」を振り返る(18):

1976年にIntelで開発された製品のうち、最も重要だと思われるのが、マイクロコントローラー「MCS-48」だ。MCS-48の3つのファミリーを取り上げる。

福田昭のデバイス通信(184) Intelの「始まり」を振り返る(17):

前回に引き続き、1976年の主な出来事を紹介する。この年にIntelが出荷したメモリは、4Kビット換算で1200万個を超えた。また、マイクロプロセッサ事業を強化すべく、同部門を独立させている。

福田昭のデバイス通信(183) Intelの「始まり」を振り返る(16):

Intelの創業9年目となる1976年は、業績が回復するとともに、従業員数が大幅に増加した年でもあった。

福田昭のデバイス通信(182) Intelの「始まり」を振り返る(15):

引き続き、1975年に焦点を当てる。今回は、1975年にIntelの社長を始めとする経営幹部の顔ぶれがかなり変化したことと、その内容を説明する。

福田昭のデバイス通信(181) Intelの「始まり」を振り返る(14):

前回に続き、1975年に焦点を当てる。この年、Intelにとって初めての海外工場となるマレーシア・ペナン工場で火災が発生した。工場はわずか1時間で全焼。工場再建までの間、Intelは他社の製造ラインを「時間買い」することで急場をしのいだ。

福田昭のデバイス通信(180) Intelの「始まり」を振り返る(13):

今回は、創業8年目となる1975年の業績を紹介する。この年は売り上げの伸びが鈍化し、営業利益と純利益は前年比18%減と、初めての減益となった。

福田昭のデバイス通信(179) Intelの「始まり」を振り返る(12):

引き続き、創業7年目である1974年の状況を紹介する。今回は、クオーツ式腕時計に関連する事業の活動を主に紹介する。

福田昭のデバイス通信(178) Intelの「始まり」を振り返る(11):

Intelの創業7年目となる1974年を取り上げる。この年にIntelが発売した8ビットマイクロプロセッサ「8080」は、初期のパソコンを生み出すことになる、歴史歴な半導体製品だった。

福田昭のデバイス通信(177) Intelの「始まり」を振り返る(10):

今回は、Intel創業7年目となる1974年の半導体メモリに関連する状況を解説する。

福田昭のデバイス通信(176) Intelの「始まり」を振り返る(9):

Intelの創業7年目(1974年)に焦点を当てる。業績は極めて好調で、収入が1億米ドルを超えた。一方で四半期業績にはピークと低下がみられ、「シリコン・サイクル」が登場していることが分かる。

福田昭のデバイス通信(175) Intelの「始まり」を振り返る(8):

Intelの創業6年目となる1973年。この年に関してはなぜか年次報告書が掲載されていないので、業績のみを紹介する。それに加えて、クリーンルームにまつわる驚きのエピソードにも触れたい。

福田昭のデバイス通信(174) Intelの「始まり」を振り返る(7):

Intelの創業5年目となる1972年。この年で特筆すべきは、Intelが電子式腕時計の開発ベンチャーであるMicromaを買収し、子会社としたことだろう。

福田昭のデバイス通信(173) Intelの「始まり」を振り返る(6):

Intelの創業5年目となる1972年は、同社にとって記念すべき年となった。創業以来、初めて黒字になったのである。

福田昭のデバイス通信(172) Intelの「始まり」を振り返る(5):

Intelの創業4年目となる1971年。後編では、赤字が急速に縮小し、創業以降で初めての最終黒字となるまでの経緯を追う。

福田昭のデバイス通信(171) Intelの「始まり」を振り返る(4):

Intelの創業4年目(1971年)は、「飛躍の年」となった。不揮発性メモリとマイクロプロセッサという、2つの画期的な製品を開発したのだ。前編では、この2製品と、本社社屋の移転について紹介する。

福田昭のデバイス通信(170) Intelの「始まり」を振り返る(3):

Intelの創業3年目となる1970年。「3101」と「1101」の2つのSRAMを開発したことで、Intelは売り上げを急激に拡大していく。

福田昭のデバイス通信(169) Intelの「始まり」を振り返る(2):

創業翌年となる1969年。創業後わずか9カ月で製品の開発を完了させたIntelだったが、資金繰りは厳しかった。1969年における最終損失は前年の4.3倍に増大している。

福田昭のデバイス通信(168) Intelの「始まり」を振り返る(1):

ことし、2018年に創業50周年を迎えたIntel。半導体専業メーカーで半世紀にわたって存続し続けた企業は非常に珍しい。そこで、今回から、Intelに焦点を当てる。Intelの公式文書である「年次報告書(アニュアルレポート)」をベースに、Intelの創業当時の活動を1年ずつ、記述していく。

福田昭のデバイス通信(167) imecが語る最新のシリコンフォトニクス技術(27):

本シリーズ最終回となる今回は、量子井戸半導体レーザーについて解説する。試作したレーザーのテスト結果の他、課題などを紹介する。

福田昭のデバイス通信(166) imecが語る最新のシリコンフォトニクス技術(26):

本シリーズも、いよいよ最終章となる。最後は、シリコン基板に、化合物半導体レーザーをモノリシックに集積する試みを、前後編にわたって解説する。

福田昭のデバイス通信(165) imecが語る最新のシリコンフォトニクス技術(25):

今回は、光送受信システムのリンクバジェットを計算した事例を説明する。

福田昭のデバイス通信(164) imecが語る最新のシリコンフォトニクス技術(24):

今回は、光変調器を高速で駆動する電気回路、すなわちシリコンCMOSのドライバ回路を試作した事例を説明する。

福田昭のデバイス通信(163) imecが語る最新のシリコンフォトニクス技術(23):

今回は、試作した光送受信モジュール(光トランシーバー)と光ファイバーを結合する技術と、試作品の外観写真、動作性能を解説する。

福田昭のデバイス通信(162) imecが語る最新のシリコンフォトニクス技術(22):

今回は、16チャンネルの光送受信モジュール(光トランシーバー)の試作例を紹介する。試作した光トランシーバーは、1チャンネル当たり56Gbpsの速度で光信号を変調する。つまり、16チャンネルの合計では、896Gbpsの帯域幅を実現できることになる。

福田昭のデバイス通信(161) imecが語る最新のシリコンフォトニクス技術(21):

今回は、超高速光送受信器(光送受信モジュール)の構成例を紹介する。

福田昭のデバイス通信(160) imecが語る最新のシリコンフォトニクス技術(20):

光送受信器の構造と性能向上(スケーリング)について解説する。性能向上の手法は主に、高速化、多値化、多チャンネル化の3つの方向性がある。

福田昭のデバイス通信(159) imecが語る最新のシリコンフォトニクス技術(19):

後編では、半導体レーザーとシリコン光導波路を接続する技術のうち、シリコンウエハーにレーザーダイを貼り付ける「ダイ・ウエハー・ボンディング」と、シリコンウエハーにレーザーダイをフリップチップ接続する「フリップチップ・レーザー」について解説する。

福田昭のデバイス通信(158) imecが語る最新のシリコンフォトニクス技術(18):

今回は、光源となる半導体レーザーとシリコン光導波路を結合する技術を解説する。

福田昭のデバイス通信(157) imecが語る最新のシリコンフォトニクス技術(17):

今回は、光ファイバーとシリコン光導波路を結合する技術を解説する。

福田昭のデバイス通信(156) imecが語る最新のシリコンフォトニクス技術(16):

今回は、100Gビット/秒(bps)と極めて高速な変調信号を光ファイバーで伝送する実験結果を紹介する。

福田昭のデバイス通信(155) imecが語る最新のシリコンフォトニクス技術(15):

今回は、光信号を電気信号に変換する「光検出器」について解説するとともに、ゲルマニウム光検出器の試作品について動特性を示す。

福田昭のデバイス通信(154) imecが語る最新のシリコンフォトニクス技術(14):

電界吸収変調器(EA変調器)を試作して測定した、静特性と動特性の結果を解説する。さらに、EA変調器の他、マッハツェンダ変調器(MZ変調器)とリング変調器のベンチマーク結果をまとめる。そこから分かることは何だろうか。

福田昭のデバイス通信(153) imecが語る最新のシリコンフォトニクス技術(13):

今回は、エレクトロアブソープション効果(フランツケルディッシュ効果)を利用する変調器(EA変調器)を解説する。さらに、EA変調器でゲルマニウムシリコン(GeSi)を使う理由も併せて説明する。

福田昭のデバイス通信(152) imecが語る最新のシリコンフォトニクス技術(12):

「マッハツェンダ変調器(MZ変調器)」と「リング変調器」の試作例を取り上げ、構造と性能を紹介する。

福田昭のデバイス通信(151) imecが語る最新のシリコンフォトニクス技術(11):

シリコンフォトニクスの代表的な光変調器「マッハツェンダ変調器(MZ変調器)」と「リング変調器」の基本原理である、シリコン半導体中のキャリア密度によって屈折率が変わる様子を解説する。

福田昭のデバイス通信(150) imecが語る最新のシリコンフォトニクス技術(10):

前回、光信号の振幅や位相などを連続的に変化させるデバイス「光変調器」の基礎を説明した。今回からは、光変調器の具体的な解説に入る。

福田昭のデバイス通信(149) imecが語る最新のシリコンフォトニクス技術(9):

今回から、光信号の振幅や位相などを変化させる能動素子「光変調器」を解説していく。光の変調方式は、「直接変調」と「外部変調」に大別される。それぞれについて説明していこう。

福田昭のデバイス通信(148) imecが語る最新のシリコンフォトニクス技術(8):

波長分割多重(WDM)伝送に必須の受動素子である光波長フィルターの特性と、その制御について解説する。

福田昭のデバイス通信(147) imecが語る最新のシリコンフォトニクス技術(7):

光回路を形成する受動素子(パッシブデバイス)を解説する。具体的にはシリコン光導波路と、基本的なシリコン光波長フィルターを取り上げる。

福田昭のデバイス通信(146) imecが語る最新のシリコンフォトニクス技術(6):

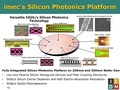

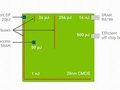

今回は、imecのシリコンフォトニクス・プラットフォームを解説する。このプラットフォームは、200mm(8インチ)あるいは300mm(12インチ)のシリコンウエハーに、ありとあらゆる光部品を作り込もうとするものだ。

福田昭のデバイス通信(145) imecが語る最新のシリコンフォトニクス技術(5):

今回は、実装技術と光送受信モジュール技術のロードマップを解説する。光送受信モジュールの高速化と広帯域化では、波長分割多重(WDM)技術が重要になってくる。

福田昭のデバイス通信(144) imecが語る最新のシリコンフォトニクス技術(4):

今回は、シリコンフォトニクスの技術開発ロードマップを解説する。シリコンフォトニクスの性能向上とコストを、16/14nmから5nm、3nmの技術ノードに沿って見ていこう。

福田昭のデバイス通信(143) imecが語る最新のシリコンフォトニクス技術(3):

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。

福田昭のデバイス通信(142) imecが語る最新のシリコンフォトニクス技術(2):

データセンターで信号伝送を担うのは、銅ケーブル(電気通信)と光ファイバーケーブル(光ファイバー通信)だ。今回は、この2つにおける通信速度と通信距離の関係や、光ネットワークの帯域を向上する上で鍵となる技術を解説する。

福田昭のデバイス通信(141) imecが語る最新のシリコンフォトニクス技術(1):

今回から、「IEDM 2017」で開催されたチュートリアルから、シリコンフォトニクス技術を紹介する。まずは、光ファイバー通信の基礎から始めていこう。

福田昭のデバイス通信(140):

半導体メモリの場合、1個のパッケージあるいはチップに搭載されているシリコンダイは、1個(1枚)とは限らない。多い時には16枚という場合もある。シリコンダイの枚数を知るには、いくつか方法がある。

福田昭のデバイス通信(139):

「チップ」「デバイス」という単語から想像するイメージは、業界やコミュニティーによってずれがある。では、どのようなずれがあり、なぜ、ずれが生じたのだろうか。

福田昭のデバイス通信(138):

2017年12月のこと。米国サンフランシスコで開催される「IEDM 2017」で、米国ハワイで2018年6月に開催する「VLSIシンポジウム」の非公式ブリーフィングを行うという、何とも不思議な案内状が届いた。一体、どういうことだったのか。

福田昭のデバイス通信(137) 2月開催予定のISSCC 2018をプレビュー(13):

「ISSCC 2018」の技術講演を紹介するシリーズ、最終回となる今回は、最終日のセッション28〜31を紹介する。東芝グループは次世代の無線LAN技術「802.11ax」に対応する送受信SoC(System on a Chip)を発表する。その他、114本の短針プローブによって脳神経信号を並列に取得するシステムや、カーボンナノチューブFETとReRAMによる脳型コンピューティング回路などが発表される。

福田昭のデバイス通信(136) 2月開催予定のISSCC 2018をプレビュー(12):

今回は「ISSCC 2018」最終日午後から、セッション26と27の注目講演を紹介する。0.56THzを検出するセンサーアレイシステムや、過渡回復時間が6マイクロ秒の昇降圧型DC-DCコンバーターなどが登場する。

福田昭のデバイス通信(135) 2月開催予定のISSCC 2018をプレビュー(11):

「ISSCC 2018」最終日の技術講演から、セッション23〜25のハイライトをお届けする。周波数が300GHzと極めて高い発振器の他、GaNデバイスを駆動する電源回路技術、5GHzのクロックを発生する回路などが紹介される。

福田昭のデバイス通信(134) 2月開催予定のISSCC 2018をプレビュー(10):

「ISSCC 2018」最終日午前の技術講演から、セッション21と22を紹介する。データ転送速度が10Gビット/秒で消費電力が150μWのシリコンフォトニクス送受信回路や、72Gサンプル/秒の8ビットSAR型A-D変換回路などについて、開発成果が披露される。

福田昭のデバイス通信(133) 2月開催予定のISSCC 2018をプレビュー(9):

「ISSCC 2018」最終日午前の講演から、セッション19と20を紹介する。シリコン面積が0.00021平方mmと極めて小さな温度センサーや、3D(3次元) NANDフラッシュメモリの大容量化および高密度化についての論文が発表される。

福田昭のデバイス通信(132) 2月開催予定のISSCC 2018をプレビュー(8):

「ISSCC 2018」技術講演の最終日、午前は8本のセッションが予定されている。プロセス、電圧、温度、時間経過による変動を補償する電源回路や、低消費電力で高速のLDOレギュレーター技術に関する研究成果が発表される。

福田昭のデバイス通信(131) 2月開催予定のISSCC 2018をプレビュー(7):

前回に続き、「ISSCC 2018」2日目午後の技術講演から、見どころを紹介する。低消費電力の2.4GHz帯無線端末用PLL回路や、全天周をVGA解像度で撮影するカプセル内視鏡などが登場する。

福田昭のデバイス通信(130) 2月開催予定のISSCC 2018をプレビュー(6):

「ISSCC 2018」2日目午後の技術講演から、見どころを紹介する。SRAMダイとDNN(深層ニューラルネットワーク)推論エンジンを積層した機械学習チップや、消費電力が4.5μWと極めて低い15ビットA-D変換器チップなどの研究論文が発表される。

福田昭のデバイス通信(129) 2月開催予定のISSCC 2018をプレビュー(5):

「ISSCC 2018」2日目午前に行われるセッションのうち、セッション9〜12の見どころを紹介する。76GHz〜81GHz帯を使用する車載用ミリ波レーダー送受信回路や、超小型の慣性式ナビゲーションシステム、GDDR6準拠の16GビットDRAMなどが登場する。

福田昭のデバイス通信(128) 2月開催予定のISSCC 2018をプレビュー(4):

「ISSCC 2018」2日目午前から、注目講演を紹介する。低ジッタのクロック回路技術や、2.4GHz帯のWi-Fi電波からエネルギーを収穫する環境発電回路などについての講演が発表される。

福田昭のデバイス通信(127) 2月開催予定のISSCC 2018をプレビュー(3):

「ISSCC 2018」技術講演の初日(2018年2月12日)。午後のハイライトとして、ミリ波無線、イメージセンサー、超高速有線通信をテーマにした注目論文を紹介する。ミリ波無線では「IEEE 802.11ad」に準拠した送受信回路チップが登場。イメージセンサーでは、ソニーやパナソニックが研究成果を披露する。有線通信では、PAM-4によって100Gビット/秒の通信速度を実現できる回路が発表される。

福田昭のデバイス通信(126) 2月開催予定のISSCC 2018をプレビュー(2):

「ISSCC 2018」技術講演の初日(2018年2月12日)。午後のハイライトは、最先端のプロセッサおよびアナログ技術の論文発表だ。プロセッサでは、IntelやIBM、AMDが、アナログ技術ではQualcommやMediaTekが、それぞれの研究成果を披露する。

福田昭のデバイス通信(125) 2月開催予定のISSCC 2018をプレビュー(1):

毎年2月に開催される、半導体チップの回路技術とシステム技術に関する国際学会「ISSCC(国際固体回路会議)」。えり抜きの論文が発表される重要なイベントだ。今回から始まる本シリーズでは、開催を2カ月後に控えたISSCCについて、概要と注目論文を紹介する。

福田昭のデバイス通信(124) 12月開催予定のIEDM 2017をプレビュー(8):

これまで7回にわたり「IEDM 2017」の概要と注目の技術講演を紹介してきた。今回はIEDM 2017レビュー編の最終回として、開催最終日である12月6日午後のセッションから注目講演を紹介する。

福田昭のデバイス通信(123) 12月開催予定のIEDM 2017をプレビュー(7):

12月6日午前のセッションから、注目講演を紹介する。メモリセルと論理演算を統合することで脳神経回路を模倣する研究の成果や、10nm/7nm世代のCMOSロジック量産技術についての発表が行われる。

福田昭のデバイス通信(122) 12月開催予定のIEDM 2017をプレビュー(6):

12月5日午後の注目講演を紹介する。負性容量トランジスタ、シリコンフォトニクス、非シリコン材料による高耐圧パワーデバイスなどの研究成果が発表される。

福田昭のデバイス通信(121) 12月開催予定のIEDM 2017をプレビュー(5):

今回から、12月5日午後の注目講演を順次紹介していく。電荷ベースのメモリ、最先端CMOSのさらなる微細化手法、最先端の金属ゲート技術やコンタクト技術など、興味深いテーマが並ぶ。

福田昭のデバイス通信(120) 12月開催予定のIEDM 2017をプレビュー(4):

2017年12月5日午前のセッションから注目講演を紹介する。ソニーは、スマートフォン向けを想定した、シリコンの赤外線イメージセンサーについて発表する。その他、III-V族ナノスケールMOSFETや、バイオセンサー、化学センサーなどの講演を取り上げる。

福田昭のデバイス通信(119) 12月開催予定のIEDM 2017をプレビュー(3):

「IEDM 2017」について、技術講演の2日目となる12月5日の午前のセッションから注目講演を紹介する。モアムーアやモアザンムーアを進めていくときの課題や、オールカーボンの次世代多層配線などが発表される。

福田昭のデバイス通信(118) 12月開催予定のIEDM 2017をプレビュー(2):

技術講演初日である2017年12月4日から、注目の講演を紹介する。抵抗変化メモリ(ReRAM)や、折り曲げ可能な電子回路(フレキシブルエレクトロニクス)関連で、興味深い講演が多い。

福田昭のデバイス通信(117) 12月開催予定のIEDM 2017をプレビュー(1):

ことしも「IEDM」の季節がやってきた。最先端電子デバイスの研究開発に関する国際学会「IEDM 2017」が、12月に米国で開催される。本シリーズでは、概要と注目の技術講演を紹介していく。

福田昭のデバイス通信(116):

今回は、パッケージングの組み立て工程(後工程)に関する市場規模などに触れつつ、パッケージ組み立て請負サービス企業(SATS)の再編成について紹介する。

福田昭のデバイス通信(115):

半導体製造工程における「後工程」を担うパッケージング産業の再編成が起こっている。今回から2回にわたり、パッケージ産業再編の動きを紹介する。

福田昭のデバイス通信(114) TSMCが解説する最先端パッケージング技術(13):

本シリーズの最後として紹介するのは「ESP(Embedded Substrate Packaging)」だ。その名の通り、多層プリント基板にICや受動部品を埋め込む技術である。電源モジュールや高周波無線モジュールでの採用が多く、これらモジュールの小型化に貢献してきた。

福田昭のデバイス通信(113) TSMCが解説する最先端パッケージング技術(12):

前回説明したウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」における一括製造の考え方を、パネル状の基板に適用したのが、パネルレベルのファンアウトパッケージング技術「FOPLP(Fan-Out Panel Level Packaging)」だ。今回は、FOPLPの強みや、どんなパッケージングに適しているかなどを説明する。

福田昭のデバイス通信(112) TSMCが解説する最先端パッケージング技術(11):

前回に引き続き、ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」を取り上げる。今回はTSMCなど各社のFOWLPによるパッケージ開発事例を見ていく。

福田昭のデバイス通信(111) TSMCが解説する最先端パッケージング技術(10):

ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程は、開発企業によって大きく異なる。そこで、いくつかに大別される製造工程の違いを紹介する。

福田昭のデバイス通信(110) TSMCが解説する最先端パッケージング技術(9):

今回から、モバイル端末向けのパッケージング技術について解説する。大きく分けて、ウエハーレベルのファンアウトパッケージング(FOWLP)、パネルレベルのファンアウトパッケージング(FOPLP)、プリント基板へ回路素子を埋め込むパッケージング(ESP)がある。まずは、パッケージング技術における「ファンアウト」の意味を確認しつつ、Infineon Technologiesが開発した“元祖FOWLP”を説明したい。

福田昭のデバイス通信(109) TSMCが解説する最先端パッケージング技術(8):

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。

福田昭のデバイス通信(108) TSMCが解説する最先端パッケージング技術(7):

シリコンインターポーザを導入したパッケージの製品化時期は、おおむね、2012年の第1期と、2015〜2016年の第2期に分けられる。それぞれの時期を代表する製品例と、それらの特徴を紹介する。

福田昭のデバイス通信(107) TSMCが解説する最先端パッケージング技術(6):

「CoWoS(Chip on Wafer on Substrate)」の解説の後編では、パッケージの構造とパッケージの製造工程について説明する。パッケージの信頼性を大きく左右するのが、シリコンインターポーザの反りだが、CoWoSの製造工程では、この反りを抑えることができる。

福田昭のデバイス通信(106) TSMCが解説する最先端パッケージング技術(5):

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。

福田昭のデバイス通信(105) TSMCが解説する最先端パッケージング技術(4):

2012年ごろから、主に高性能コンピューティング(HPC)分野では「CoWoS(Chip on Wafer on Substrate)」の製品化が進んだ。その最大の特長であるシリコンインターポーザは優れた技術なのだが、コストが高いのが難点だった。そのため、CoWosの低コスト版ともいえる2.nD(2.n次元)のパッケージング技術の提案が相次いだ。

福田昭のデバイス通信(104) TSMCが解説する最先端パッケージング技術(3):

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。

福田昭のデバイス通信(103) TSMCが解説する最先端パッケージング技術(2):

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。

福田昭のデバイス通信(102) TSMCが解説する最先端パッケージング技術(1):

システムを複数のチップに分けてから高密度に集積化したパッケージは、SiP(System in Package)と呼ばれる。「ムーアの法則」を拡張するために、新しいSiP技術あるいはパッケージング技術が次々に登場している。今回から始まる新シリーズでは、こうした新しいパッケージング技術を紹介したい。

福田昭のデバイス通信(101) 高性能コンピューティングの相互接続技術(6):

相互接続(インターコネクト)のエネルギー効率を高める技術の1つである「バランス型電荷再利用バス(BCRB:Balanced Charge Recycling Bus)」。今回は、BCRB技術のバスを搭載したテストチップの概要と、実験結果について解説する。

福田昭のデバイス通信(100) 高性能コンピューティングの相互接続技術(5):

相互接続(インターコネクト)に電荷再利用型バス(Charge Recycling Bus)を利用すると、エネルギー効率を高めることができる。だが、電荷再利用型バスにも弱点は存在する。今回は、電荷再利用型バスの課題とそれを解決する技術を紹介しよう。

福田昭のデバイス通信(99) 高性能コンピューティングの相互接続技術(4):

バスやリンクなどの相互接続(インターコネクト)は大きなエネルギーを消費する。では、どのようにして消費電力を下げ、エネルギー効率を高めればよいのか。前編では、信号振幅を小さくする方法と、電荷を再利用する方法の2つについて解説する。

福田昭のデバイス通信(98) 高性能コンピューティングの相互接続技術(3):

後編では、修正版のデナード・スケーリングを解説する。修正版のデナード・スケーリングでは、微細化によってMOSFETの密度は2倍に増えるものの、動作速度は高くならず、消費電力は1.4倍となる。そのため、消費電力を増やさないためには、MOSFETの密度を2倍ではなく、1.4倍にとどめる必要があるのだ。

福田昭のデバイス通信(97) 高性能コンピューティングの相互接続技術(2):

1970年代から1990年代にかけて、半導体集積回路は「デナード・スケーリング」という法則に沿って高密度化と高速化を達成してきた。今回は、デナード・スケーリングの内容と、なぜ1990年代以降は、この法則に沿って微細化を進めることが困難になったのかを説明する。

福田昭のデバイス通信(96) 高性能コンピューティングの相互接続技術(1):

2016年12月に米国サンフランシスコで開催された「IEDM2016」。そのショートコースから、NVIDIAの講演を複数回にわたり紹介する。初回となる今回は、コンピュータ・システムにおいてデータのやりとりに消費されるエネルギーをなぜ最小化する必要があるのか、その理由を28nm CMOSプロセスで製造したSoCを用いて説明しよう。

福田昭のデバイス通信(95):

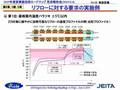

前回に続き、5nm世代のロジック配線プロセスを展望したimecの講演を紹介する。後編となる今回は、微細化に対応して配線抵抗(R)と配線容量(C)を最適化する方法について解説する。

福田昭のデバイス通信(94):

imceによる、5nm世代のロジック配線プロセスを展望した講演を、前後編の2回にわたりお届けする。前半では、配線抵抗(R)、配線容量(C)、RC積という配線のパラメータの特徴を紹介する。さらに、10nm世代、7nm世代、5nm世代と微細化が進むと、配線抵抗(R)、配線容量(C)、RC積がどのように変化していくかを解説する。

福田昭のデバイス通信(93):

Synopsysの講演では、5nm世代のトランジスタのシミュレーション評価結果が報告された。この結果からはFinFETの限界が明確に見えてくる。5nm世代に限らず、プロセスの微細化が進むと特に深刻になってくるのが、トランジスタ性能のばらつきだ。

福田昭のデバイス通信(92):

Applied Materialsの講演では、MOSFETの微細化ロードマップと、微細化の手法および課題が解説された。7nm世代のFinFETでは、フィンを狭く、高くするとともにコンタクト用の金属材料を変える必要が出てくる。FinFETの限界が見え始める5nm世代では、微細化の手法として主に2つの選択肢がある。

福田昭のデバイス通信(91):

Samsung Semiconductorの講演では、「ムーアの法則」の現状認識から始まり、同社が考える微細化のロードマップが紹介された。Samsungは28nm世代と10nm世代が長く使われると予想している。さらに同社は、EUVリソグラフィが量産レベルに達するのは2018年で、7nm/5nm世代のチップ製造に導入されるとみている。

福田昭のデバイス通信(90):

imecは次世代のリソグラフィ技術を展望するフォーラムの講演で、半導体デバイスの微細化ロードマップを披露した。このロードマップでは、微細化の方向が3つに整理されている。シリコンデバイスの微細化、シリコン以外の材料の採用、CMOSではないデバイスの採用だ。imecは、CMOSロジックを微細化していく時の課題についても解説した。

福田昭のデバイス通信(89):

大手レジストベンダーJSR Microの講演では、主に同社とimecの共同開発の内容が発表された。その1つが、JSR MicroのEUV(極端紫外線)レジストをimec所有のEUV露光装置で評価するというもので、化学増幅型のEUVレジストによってハーフピッチ13nmの平行直線パターンを解像できたという。さらに、5nm世代のEUVリソグラフィの目標仕様と現状も紹介された。

福田昭のデバイス通信(88):

「SEMICON West 2016」で行われた次世代のリソグラフィ技術を展望するフォーラムから、各露光装置メーカーの講演内容を紹介してきた。今回は、半導体露光装置最大手であるASMLのEUV(極端紫外線)リソグラフィ開発状況を中心に紹介する。

福田昭のデバイス通信(87):

今回は、7nm世代以降の半導体製造プロセスで使わざるを得なくなるだろう「自己整合(セルフアライン)的なリソグラフィ技術」に触れる。その候補は3つ。東京エレクトロンのBen Rathsack氏が、3つの候補技術の現状を紹介した。

福田昭のデバイス通信(86):

90nm世代から商業化が始まったArF液浸スキャナーだが、3xnm世代に入ると、解像力は限界に達する。そこで、コスト増というデメリットは伴うものの、マルチパターニングによって解像力の向上が図られてきた。加えて、7nm世代向けのArF液浸スキャナーでは新しいリソグラフィ技術の導入も必要だとされている。この場合、コスト面ではダブルパターニングと電子ビーム直接描画の組み合わせが有利なようだ。

福田昭のデバイス通信(85):

KrFスキャナーの次に登場したのがArFスキャナーである。ArFスキャナーは90nm世代の量産から使われ始めた。さらに、ArFスキャナーの製品化と並行して「ポストArF」の開発が活発化する。ポストArFとして、F2エキシマレーザーあるいは軟X線を光源とする露光技術の開発が進んだが、そこに、もう1つの候補として急浮上したのがArF「液浸」スキャナーである。

福田昭のデバイス通信(84):

今回は、半導体露光技術の歴史の完結編(その1)をお届けする。1996年ごろに本格的に導入され始めたKrFステッパーだが、既に2つの課題が浮上していた。光学系の開口数(N.A.)の向上の限界と、シリコンダイが大きくなり過ぎていたことだ。これらを解決する手段として登場したのが「スキャナー」である。

福田昭のデバイス通信(83):

今回はステッパー(縮小投影分割露光装置)の進化の歴史をたどる。1980〜1990年代半ばにかけて、g線ステッパーでは光学系の開口数(N.A.)が順調に向上し、i線ステッパーへと移行していく。その後、1996〜1997年になると、量産に使えるKrFレーザーステッパーが登場する。

福田昭のデバイス通信(82):

今回は、等倍一括露光から縮小分割露光への転換の歴史を紹介する。縮小分割露光は、光露光技術の画期的なブレークスルーであった。そしてこの技術は、ニコンが半導体露光装置メーカーの大手へと成長するきっかけにもなった。

福田昭のデバイス通信(81):

今回から、リソグラフィ技術のセッションの概要を紹介する。まずは、半導体露光技術の進化について解説したい。前半では主に、「コンタクト露光」から始まる等倍露光技術の発展の流れを見てみよう。

福田昭のデバイス通信(80):

前回に続き、半導体産業の市場について解説する。半導体製造装置の市場規模は3年前の2013年に比べて増加しているが、地域別にみると中国の台頭が目立つ。また、同市場の成長要因についても触れる。

福田昭のデバイス通信(79):

米国で開催された「SEMICON West 2016」の記者説明会から、SEMIによる半導体の市場動向を紹介する。前編となる今回は、半導体デバイスと半導体製造装置の市場動向について説明する。

福田昭のデバイス通信(78):

半導体製造関連の北米最大の展示会「SEMICON West 2016」が現在、カリフォルニア州サンフランシスコで開催中だ。今回のテーマは「これまでのビジネスは忘れろ」。そこから見えてくるのは、半導体産業が明らかに転換期に入ったということだ。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(16):

ARM Researchの講演内容を紹介してきたシリーズ。完結編となる今回は、ARMが「スーパーメモリ」と呼ぶ“理想的なメモリ”の仕様を紹介したい。現時点で、このスーパーメモリに最も近いメモリは、どれなのだろうか。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(15):

ここ数回にわたり「SRAMについて知っておくべきこと」を紹介している。今回は、SRAMの書き込み動作について説明していこう。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(14):

今回は、SRAMの消費電力と設計課題について解説する。SRAMの低消費電力化に効果的なのは電源電圧を下げることだが、これには、書き込み不良と読み出しディスターブ不良という問題が付きまとう。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(13):

今回からはSRAMについて知っておくべきことを紹介していく。まずは、多くの半導体メモリにも共通するSRAMシリコンダイの基本レイアウトから説明していこう。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(12):

今回は、HBM(High Bandwidth Memory)とDDR4 DRAMを、データ転送速度やパッケージングなどの点から比較してみる。後半は、埋め込みDRAM(eDRAM)の説明に入る。ARM ReserchのRob Aitken氏は、eDRAMが「ニッチな市場にとどまる」と予想しているが、それはなぜだろうか。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(10):

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(9):

今回は、仮想メモリの仕組みを詳しく解説していこう。仮想メモリの概要と、これを採用したシステムについて見てみたい。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(8):

今回は、メモリアクセスの高速化手法である「投機的プリフェッチ(Speculative Prefetch)」の仕組みを解説する。これは、“次のアクション”を推測して、データをキャッシュにコピーするものだ。この他、キャッシュが抱える本質的な弱点についても触れておきたい。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(7):

今回は、キャッシュメモリの基本動作について解説する。基本動作は、大きく分けて2つある。メインメモリからデータをキャッシュラインにコピーする「アロケーション」と、特定のキャッシュラインからデータを追い出して“空き”を作る「エビクション」だ。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(6):

今回は、キャッシュメモリについて解説する。キャッシュの考え方はとてもシンプルだが、実装となるとさまざまな方法があって複雑だ。今回は、3つのキャッシュアクセス構造について説明しよう。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(5):

今回から、CPUアーキテクチャとメモリ・システムの関連について掘り下げていこう。まずは5段パイプラインアークテクチャを例に挙げ、メモリ・システムとの関連をみていく。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(4):

今回は、NANDフラッシュメモリ登場後のメモリ・アーキテクチャを見ていきながら、「CPUのメモリに対する要求」を考えていく。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(3):

今回からは、「CPUのメモリに対する要求」について紹介していく。まずは、CPUのアーキテクチャがどのように変ってきたかを振り返りつつ、CPUのメモリに対する要求の変遷を見ていこう。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(2):

システム設計において、CPUコアはもはやそれほど重要ではない。大切なのは、メモリ、相互接続(配線)、消費電力、ソフトウェアである。ディスプレイを例に挙げ、最適なシステム・アーキテクチャの構築について説明しよう。

福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(1):

今回から、2015年12月に開催された「IEDM2015」でARM Researchが講演した、メモリ技術の解説をお届けしよう。まずは、システム設計が抱える課題から紹介していきたい。

福田昭のデバイス通信(61):

前編に続き、IntelとMicron Technologyの次世代不揮発性メモリ「3D XPoint」について解説しよう。今回は、「オボニック・スレッショルド・スイッチ(OTS:Ovonic Threshold Switch)」と、材料について詳しく見ていきたい。

福田昭のデバイス通信(60):

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。

福田昭のデバイス通信 ISSCC 2016プレビュー(10):

10回にわたりお届けしてきた「ISSCC 2016」プレビュー。最終回となる今回は、セッション27と28のおすすめ講演を紹介する。セッション28の主要テーマは医療エレクトロニクスだ。バッテリーで動作し、持ち運びが可能な生体信号計測システムなどが発表される。

福田昭のデバイス通信 ISSCC 2016プレビュー(9):

今回はセッション24〜26を紹介する。「ワイヤレス通信」がテーマとなっているセッション24では、IoE(Internet of Everything)向けの低消費電力無線チップの発表が相次ぐ。ソニーとソニーLSIデザインが開発した、消費電力が1.5mW〜2.3mWと低いGNSS(全地球航法衛星システム)受信器などが発表される。

福田昭のデバイス通信 ISSCC 2016プレビュー(7):

今回はセッション19〜21までを紹介する。セッション20では、パナソニックが発表する、300GHz帯で32値のQAM信号を出力する送信器チップに注目したい。チャンネル当たりのデータ送信速度は17.5Gビット/秒で、6チャンネルの5GHz帯域出力を備えている。

福田昭のデバイス通信 ISSCC 2016プレビュー(6):

セッション17とセッション18のテーマはメモリだ。セッション17では、Samsung Electronicsが、10nmのFinFETを用いた高密度SRAMの開発成果を披露する。メモリセルの面積が0.04μm2と、過去最小のSRAMセルを実現している。

福田昭のデバイス通信 ISSCC 2016プレビュー(5):

セッション15では、Analog Devices(ADI)が発表する、入力帯域幅が465MHzと極めて広いΔ-Σ方式のA/D変換器などに注目したい。2016年2月1日と2日の夜に行われる、パネル討論会も興味深い。「無線回路を20nm未満に微細化する必要はあるのか」や、「2000年代の回路設計で最も素晴らしい瞬間」などが討論のテーマだ。パネリストたちの熱い本音トークが聞けることを期待したい。

福田昭のデバイス通信 ISSCC 2016プレビュー(4):

今回はセッション12〜14を紹介しよう。セッション14では「次世代のプロセッシング」というテーマに沿って、ディープラーニング専用コアを搭載したプロセッサや、運転者の意図を予測する機能を備えたADAS(先進運転支援システム)向けSoCなど、人工知能プロセッサの発表が相次ぐ。

福田昭のデバイス通信 ISSCC 2016プレビュー(3):

セッション7のテーマは「不揮発性メモリのソリューション」だ。マイクロンジャパンとMicron Technology、Intelの共同チームが、768Gビットと極めて大きな記憶容量のNANDフラッシュメモリを発表するなど、注目の論文が相次ぐ。

福田昭のデバイス通信 ISSCC 2016プレビュー(2):

今回は、セッション4〜6のハイライトを紹介する。セッション4では、MediaTekが、ARMv8AアーキテクチャのCPUコアを10個内蔵するモバイル・プロセッサを披露する。動作周波数の違いによってCPUコアを3つのクラスタ(トライクラスタ)に分けているものだ。ルネサス エレクトロニクスは、フルHDのビデオ処理を12チャンネル実行する車載情報機器向けSoCを発表する。

福田昭のデバイス通信 ISSCC 2016プレビュー(1):

今回から、2016年1月から2月にかけて米国で開催される半導体関連の国際学会「ISSCC(IEEE International Solid-State Circuits Conference)」を紹介していく。基調講演は、ムーアの法則や5G携帯電話、自動車通信などがテーマになっている。

福田昭のデバイス通信 IEDM 2015プレビュー(13):

13回にわたりお届けしてきたIEDM 2015のプレビューは、今回が最終回となる。本稿ではセッション32〜35を紹介する。折り曲げられるトランジスタや、電子のスピンを利用した論理回路、疾患を素早く検知する人工知能ナノアレイ技術などに関連する研究成果が発表される。

福田昭のデバイス通信 IEDM 2015プレビュー(12):

カンファレンス3日目に行われるセッション30では、オリンパスが、可視光と赤外光を同時に別々の画像として撮像するマルチバンド・イメージセンサーについて講演する。セッション31では、シリコン基板上にIII-V族化合物デバイスを作成する、次世代の電子デバイスや光デバイスについての発表が相次いで行われる。

福田昭のデバイス通信 IEDM 2015プレビュー(11):

今回はセッション27〜29を紹介する。セッション29では、生体組織分析デバイスや生体モニタリングデバイスに関する講演が行われる。Columbia Universityらの研究グループは、有機材料の発光ダイオードおよび光検出器を組み合わせた、脳血流量モニタリングシステムを発表する。同システムの厚みは、わずか5μmしかない。

福田昭のデバイス通信 IEDM 2015プレビュー(10):

今回から、カンファレンス最終日のセッションを紹介する。セッション26は、「MRAM、DRAMとSRAM」をテーマに講演が進んでいく。MRAMについては計4件の論文発表があり、例えばQualcomm Technologiesらは、40nmルールのCMOSロジックに埋め込むことを想定したSTT-MRAM技術を報告する。

福田昭のデバイス通信 IEDM 2015プレビュー(9):

2015年12月8日に開催されるセッション22のテーマは「スティープスロープ・トランジスタ」だ。このトランジスタの実現手法に関する研究成果がIntelなどから発表される。同日夜のパネルディスカッションでは、オンチップの相互接続技術や、CMOS技術が直面している課題について議論が行われる予定だ。

福田昭のデバイス通信 IEDM 2015プレビュー(8):

カンファレンス2日目に予定されているセッション19〜21の内容を紹介しよう。セッション19では、折り曲げ可能なX線イメージング技術や、折り曲げ可能なNANDフラッシュメモリなど、さまざまなフレキシブルエレクトロニクス技術に関する講演が行われる。折り曲げ可能なNANDフラッシュメモリは、韓国の研究チームが発表するもので、30万回折り曲げた後でも、安定した電気接続を維持したという。

福田昭のデバイス通信 IEDM 2015プレビュー(7):

今回はセッション16〜18の講演を紹介する。セッション17では、不揮発性メモリを利用したニューロモルフィックシステム(脳神経系を模倣した低消費電力システム)の講演が相次いだ。

福田昭のデバイス通信 IEDM 2015プレビュー(6):

今回はセッション13〜15の概要を取り上げたい。セッション15では、「モア・ムーア(More Moore)」と「モアザン・ムーア(More Than Moore)」の両方に関する研究成果が発表される。「モアザン」については、フランスの研究チームが折り曲げ可能なCMOS回路を紹介する。

福田昭のデバイス通信 IEDM 2015プレビュー(5):

今回のプレビューでは、セッション10〜12の内容を紹介する。セッション11では、ルネサス エレクトロニクスやSamsung ElectronicsがSRAM関連の技術を発表する。セッション12では、第3の2Dデバイス材料として注目を集める黒リン関連の発表に注目したい。

福田昭のデバイス通信 IEDM 2015プレビュー(4):

今回のプレビューでは、セッション7〜9を紹介する。セッション7では抵抗変化メモリ(ReRAM)の信頼性に関する発表が相次ぐ。セッション8では、3次元集積回路の製造技術がテーマだ。セッション9では、富士通と東京工業大学が試作した、96GHzの周波数で出力が3W/mmと高いInAlGaN/GaN HEMTなどが発表される。

福田昭のデバイス通信 IEDM 2015プレビュー(3):

今回はセッション4〜6の講演を紹介する。セッション4では、人間の脳をモデルにした計算アーキテクチャなどが焦点となる。セッション5では3D NAND型フラッシュメモリ関連の発表が行われ、セッション6ではIGZO材料による20nmノードの高周波FETなどが発表される予定だ。

福田昭のデバイス通信 IEDM 2015プレビュー(2):

今回は、「IEDM 2015」で開催される予定のセッションから、セッション2と3を紹介する。セッション2では、IV族元素でレーザーを試作した研究成果や、GeのナノワイヤでCMOS回路を試作した研究成果が発表される。セッション3では、主にメモリ技術がテーマとなる。

福田昭のデバイス通信 IEDM 2015プレビュー(1):

今回からは、2015年12月に米国ワシントンD.C.で開催される、最先端電子デバイスの国際学会「IEDM 2015」のプレビューを紹介する。実は、ワシントンD.C.で開催されるIEDMは、今回が最後になる。

SEMICON West 2015リポート(12):

今回は、ナノインプリント・リソグラフィ技術の開発ロードマップを紹介しよう。キヤノンは現在、インプリント装置の第1世代機の開発を終えたところで、今後5年間で第2および第3世代機の開発に取り組んでいく予定だ。インプリント装置のターゲットは、NAND型フラッシュメモリとDRAM、ロジックICである。

SEMICON West 2015リポート(11):

今回は、露光の際にシリコン・ウエハー周辺部で発生する現象「パーシャルフィールド」をもう少し掘り下げて解説しよう。このパーシャルフィールドについてキヤノンは、3種類に分けて対処しているという。

SEMICON West 2015リポート(10):

ナノインプリント・リソグラフィでは、ウエハー1枚当たりの処理時間を短縮しようとすると、欠陥密度が増加する傾向にある。だが要求されるのは、生産性の向上と欠陥密度の低減だ。キヤノンは、こうした“二律背反”の要求に応えるべく、リソグラフィ技術の改良を重ねてきた。

SEMICON West 2015リポート(9):

今回は、ナノインプリント・リソグラフィを構成する要素技術の開発状況をお伝えする。ここ1年でとりわけ大きく進歩しているのが、重ね合わせ誤差と生産性(スループット)だ。重ね合わせ誤差は半分〜3分の1に低減し、スループットは2倍〜3倍に向上しているという。

SEMICON West 2015リポート(7):

今回は、ASMLのEUV(極端紫外線)露光装置の開発ロードマップを紹介する。次期主力機「NXE:3350B」は、16nmの解像を目標に開発が進んでいるという。「NXE:33x0」シリーズとしては、2016年には光源出力を250W、生産性を1500枚/日に向上させるなど、強気な目標を立てている。

SEMICON West 2015リポート(6):

今回は、EUV(極端紫外線)露光装置の開発の歴史を振り返ってみたい。ASMLが顧客向けに初めてEUV露光装置を出荷したのは2006年のことである。その後の約10年で、光源の出力やスループットはどのくらい向上しているのだろうか。

SEMICON West 2015リポート(5):

本稿では、EUVリソグラフィ開発の進ちょくをお伝えする。ASMLの開発用露光装置「NXE:3300B」は、1日当たりのウエハー処理枚数が1000枚を超え、以前に比べるとかなり進化した。また、7nm世代のロジック配線を解像できるようになっている。

SEMICON West 2015リポート(4):

今回は、コストとパターン形成の2点について、ArF液浸とEUV(極端紫外線)リソグラフィを比べてみよう。ArF液浸では、10nm世代になるとステップ数と重ね合わせ回数が破壊的な数値に達してしまう。これがコストの大幅な上昇を招く。さらに、ArF液浸とEUVでは、10nm世代の配線パターンにも大きな差が出てくる。

福田昭のデバイス通信(36):

本シリーズは、次々世代のMOSFETで非シリコン材料がチャンネル材料の候補になっていることを説明してきた。最終回は、本シリーズのまとめであるCMOSデバイスの実現手法と試作例を紹介する。従来と同様のCMOSデバイスを非シリコン材料で実現する手法は2つある。

福田昭のデバイス通信(35):

前回は、ゲルマニウム(Ge)をチャンネル材料とするMOSFETの研究開発の歴史と現状を紹介した。今回はもう1つの材料であるインジウム・ガリウム・ヒ素(InGaAs)である。InGaAsの歴史と背景にあるIII-V族化合物半導体とともに、研究開発の状況を解説する。

福田昭のデバイス通信(34):

前回は、シリコン(Si)を代替する半導体材料の候補を紹介した。今回はゲルマニウム(Ge)をチャンネル材料とするMOSFETの研究開発の歴史と現状を紹介する。歴史上、初めてのトランジスタの材料はシリコンではなく、ゲルマニウムだった。

福田昭のデバイス通信(33):

今回からは、非シリコン材料を使ったMOSFET開発に焦点を当てる。微細化技術が行き詰まりを見せている中、非シリコンへの注目が高まっている。それはなぜなのか。また、非シリコン材料の候補には何があるのだろうか。

福田昭のデバイス通信(32):

無線センサーネットワークは、IoT(モノのインターネット)を支える基盤技術の1つだ。“IoT向け”という点を考慮すると、無線センサー端末の「完全体」というのは、外部からの充電が不要で、設置箇所に半永久的に放置できるものになるだろう。その「完全体」に近い端末を、米国のミシガン大学が試作している。

福田昭のデバイス通信(31):

シリーズ最終回となる今回は、これまでの内容をまとめてみよう。トランジスタの将来像から、消費電力と性能のバランスの取り方、微細化(スケーリング)の余地の拡大まで、ひと通り振り返る。

福田昭のデバイス通信(30):

微細化が限界を迎えた時に回路密度を向上する手法として、シリコンダイや回路層を積層する3次元技術がある。今回は、これらの手法を紹介していこう。

福田昭のデバイス通信(29):

プロセスルールの微細化において最も困難な課題は、リソグラフィ技術にある。7nm世代の半導体を量産するためのリソグラフィ技術は、いまだに確定していない。現在のところ、解決策としては、従来のArF液浸リソグラフィ技術の改善か、EUV(極端紫外光)リソグラフィ技術の開発が挙げられている。

福田昭のデバイス通信(28):

今回は、金属配線の微細化に伴う課題を取り上げる。信号の周波数当たりの配線長や、エレクトロマイグレーションといった問題があるが、これらを根本的に解決する策として期待がかかるのが、配線材料の変更や印刷エレクトロニクスの実用化である。

福田昭のデバイス通信(27):

今回はSRAMの消費電力に視点を移す。CPUの電源電圧の低下に伴うSRAMビット不良や、待機時と動作時で大きく異なるSRAMの消費電力に焦点を当て、なぜ、次世代の不揮発性メモリ「スーパーメモリ」に期待がかかっているのかを説明しよう。

福田昭のデバイス通信(26):

今回は、SRAMの微細化について触れる。16/14nm世代までは微細化が順調に進んできたが、数多くの課題が存在する。周辺回路を縮小しにくいことが、その1つとして挙げられる。

福田昭のデバイス通信(25):

今回は、トランジスタ密度をFinFETに比べて、より高められる素子の構造について触れる。代表的なものが、円筒状のチャンネルをウエハー表面と平行に配置する「ホリゾンタルナノワイヤ(HNW)」と、垂直に配置する「バーチカルナノワイヤ(VNW)」である。

福田昭のデバイス通信(24):

FinFETの“延命策”として、チャンネルの材料をシリコンからゲルマニウム(Ge)やインジウム・ガリウム・ヒ素(InGaAs)などに変更する方法がある。だが、ARMの講演では、この“延命策”に悲観的だった。今回は、Ge FETなどが抱える問題と、その打開策について紹介する。

福田昭のデバイス通信(23):

今回は、トランジスタ構造の展望を、2つの軸に沿って見ていこう。1つ目はプレーナFETからFinFETへの移行、2つ目は14nm世代から5nm世代にかけてのトランジスタ仕様である。FinFETの登場は、プレーナFETにはなかった新たな課題をもたらしている。

福田昭のデバイス通信(22):

今回は、回路の遅延時間を左右する要因について紹介する。例えば、コンタクト抵抗、しきい電圧、電源電圧、温度などがある。しきい電圧と温度、電源電圧と温度が遅延時間に与える影響はかなり複雑だが、その対処法として、DVFS(Dynamic Voltage and Frequency Scaling)技術が挙げられる。

福田昭のデバイス通信(21):

回路の動作周波数などを左右する大きな要因は「PVT」、つまりプロセス(P)、電源電圧(V)、温度(接合温度T)である。動作周波数の代表値や最高値、最低値は、PVTコーナーの数によって決まる。この数は、微細化とともに急増する傾向にあり、タイミング解析がより難しくなっている。

福田昭のデバイス通信(20):

今回は、LSI設計作業の所要時間について解説する。設計の各工程ではイタレーション、つまり「手戻り」と呼ばれる修正作業が発生する。CPUの動作周波数を上げるためには、膨大な数の手戻りが行われている。

福田昭のデバイス通信(19):

今回は、携帯機器などの用途に求められる消費電力の点から、CPUの性能を見てみよう。まず覚えておきたいのは、ゲート長ごとに性能と消費電力のトレードオフが存在するということだ。

福田昭のデバイス通信(18):

今回は、CPUコアの性能(動作周波数)とレイアウト設計の関係を見ていこう。CPUコアの性能は、レイアウト設計によって大きく変わる。CPUコアの性能とシリコン面積、消費電力は独立ではない。回路が同じでも、シリコン面積が2倍違うということもある。逆に、回路を工夫すれば、トランジスタ数を減らしてシリコン面積を削減することも可能だ。

福田昭のデバイス通信(17):

今回は、回路がどのようにレイアウトされていくのかを見てみよう。回路図が同じでも、実際にシリコンのスタンダードセルとして具現化すると、レイアウトがだいぶ異なる場合もある。ARMの講演では、コンパレータを例に取って説明していた。

福田昭のデバイス通信(16):

「スタンダードセル方式」の「スタンダード」とは、セルの高さと横幅が標準化されていることを指す。今回は、スタンダードセル方式で、高さの異なるセルを特性に応じて使い分ける方法と、同じ高さのセルで電流駆動能力を高める方法を紹介する。

福田昭のデバイス通信(15):

今回は、ロジック設計の変遷をたどっていこう。現在の主流である「スタンダード方式」の他、FPGAに代表される「セミカスタム」などがある。

福田昭のデバイス通信(14):

今回から、ARMの講演の本論に入る。論理設計から、シリコンダイに落とし込むまでに焦点を当てる。LSI設計で最も重要なのは、論理合成と配置、配線である。これらの設計品質が、“シリコンダイ”の良しあしを決める。

福田昭のデバイス通信(13):

前回、設計技術者とデバイス技術者の間には距離があることを説明した。CPUの設計者がデバイス技術者にする質問は常に同じだが、それに対するデバイス技術者の答えにはズレがあるのだ。今回は、そのズレについて説明したい。

福田昭のデバイス通信(12):

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。

福田昭のデバイス通信(11):

「デブコン大阪」の展示リポートの最後は、「オフィス」「ファクトリー」関連の技術を紹介する。オフィスの照明に可視光通信機能を組み込み、オフィス内の人間の位置情報を把握するシステムや、産業用イーサネットでモーターをリアルタイムに制御する技術などが展示された。

福田昭のデバイス通信(10):

今回は、ルネサス エレクトロニクスが最も得意とする分野、モーター制御関連の展示を紹介する。単相誘導モーターを簡単にインバータ制御に変更する技術をアピールした他、ステッピング・モーター(STPM)を永久磁石同期モーター(PMSM)に置き換えるシステムなどを展示していた。

福田昭のデバイス通信(9):

「Renesas DevCon JAPAN in Osaka」では、「ホーム(家庭)」に関する展示として、ヘルスケア通信規格「Continua(コンティニュア)」に準拠したシステムや、ペットや家族の健康状態をモニタリングするサービスなどが紹介された。

福田昭のデバイス通信(8):

今回は、都市で応用できる技術を紹介する。建物の内部劣化をインピーダンスから検知する技術や、±6°という大きなブレを調整するカメラ用の手ブレ補正技術だ。手ブレ補正は、民生機器向けではなく、インフラ向けというのがルネサスらしい。

福田昭のデバイス通信(7):

今回は、開発環境に関するソリューションを紹介する。複数の開発環境を用意しなくてもマルチコア・マイコンのデバッグが行える統合開発環境や、「RL78」マイコンのプログラムをGUIベースで自動生成するツールなどが展示された。

福田昭のデバイス通信(6):

稼働期間が十数年におよぶようなシステムの場合、保守部品の調達は常に大きな懸念点となる。最近は、供給期間をWebサイトなどで明示する半導体メーカーが増えてきた。ルネサス エレクトロニクスは、こうした取り組みを積極的に進めている。

福田昭のデバイス通信(5):

今回は、ハイエンド品である「RZファミリ」に焦点を当てる。RZファミリの特徴としてまず挙げられるのは、ARMの「Cortex」シリーズをCPUコアとして採用している点だろう。

福田昭のデバイス通信(4):

前回に続き、ルネサス エレクトロニクスの最新のマイコン群を紹介する。今回は、ミッドレンジの「RXファミリ」に焦点を当てる。

福田昭のデバイス通信(3):

ルネサス エレクトロニクスが2015年1月29日に開催した顧客向けイベント「Renesas DevCon JAPAN in Osaka」の内容を取り上げながら、同社の最新半導体ソリューションを順次、紹介していく。

福田昭のデバイス通信(2):

「ポストシリコン」の研究は、「半導体デバイスの性能を向上させるべく、非シリコン材料を使う研究」とも捉えることができる。SiC、GaNは、パワー半導体と発光デバイスでは既に採用が進んでいて、SiGeもCMOSロジック回路に導入されている。

福田昭のデバイス通信(1):

私たちの日常に欠かせないものになっているシリコン半導体。シリコン半導体は、常に“文明の利器”の進化を支え続けてきたといっても過言ではないだろう。その地位は、今後も揺るがないはずだ。

記事ランキング

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- RISC-V移行の流れ、欧州では「もう止められない」

- 「やっぱりルネサスだと言われないと」 柴田CEOが原点回帰を強調

- 「Switch 2」を分解 NVIDIAのプロセッサは温存されていた?

- SiCパワーデバイス市場は年率20%で成長、30年に103億ドル規模に

- 300mmファブ生産能力、2nmは2028年に月産50万枚へ

- 25年Q1のファウンドリー市場は縮小緩やかも、Samsung/GFは大幅低迷

- 台湾Innolux子会社がパイオニアを1636億円で買収へ

- Micronの四半期業績、売上高が過去最高を更新

- 2nm半導体設計基盤でRapidusとシーメンスが協業