MRAMの3次元積層プロセス技術を開発:大容量化と高性能化を可能に(1/2 ページ)

産業技術総合研究所(産総研)の薬師寺啓研究チーム長らは、不揮発性磁気メモリー「MRAM」の大容量化、高性能化につながる3次元積層プロセス技術を開発した。

「MRAMを製造する上でとても重要」

産業技術総合研究所(産総研)スピントロニクス研究センター金属スピントロニクスチームの薬師寺啓研究チーム長らは2017年5月、不揮発性磁気メモリー「MRAM」の大容量化、高性能化を可能とする3次元積層プロセス技術を開発したと発表した。

今回の研究は薬師寺氏の他、産総研集積マイクロシステム研究センターの高木秀樹総括研究主幹、ウエハレベル実装研究チームの倉島優一主任研究員、ナノエレクトロニクス研究部門3D集積システムグループの菊地克弥研究グループ長および、渡辺直也主任研究員らが行った。

産総研はこれまで、多結晶のMgOトンネル障壁層とCoFeB強磁性層を組み合わせた多結晶TMR素子などを開発してきた。今回は、MRAMのさらなる大容量化と高性能化に向けて、単結晶TMR薄膜をCMOS上に積層する新たな製造プロセスの開発に取り組んだ。

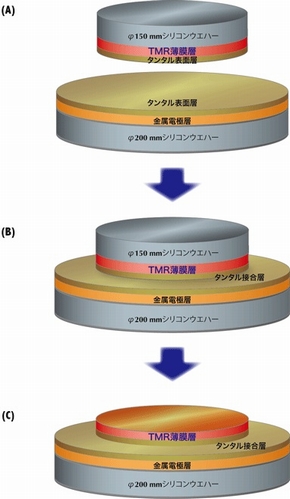

研究グループは、今回の3次元積層プロセス技術開発に当たり、単結晶TMR薄膜に比べて機械的強度が弱い多結晶TMR薄膜を用いた。実験ではまず、2種類のウエハー試料を用意した。1つは直径150mmのシリコンウエハー上に多結晶TMR薄膜層を形成した試料である。もう1つの試料には、直径200mmのシリコンウエハー上に銅電極層を形成した。2つの試料はウエハー径が異なっても問題はないという。別々に作製した2種類の試料は、それぞれ表面に金属タンタルの接合層を形成している。

次の工程であるウエハーダイレクト接合プロセスでは、両ウエハーのタンタル接合層の表面同士を合わせて接合する。最後にウエハー裏面研削プロセスで、不要となる片方のウエハーを研削により除去した。今回は、多結晶TMR薄膜層側のウエハーを除去した。これらの製造プロセスによって、200mmシリコンウエハー上に銅電極層やタンタル接合層、多結晶TMR薄膜層を積層した。

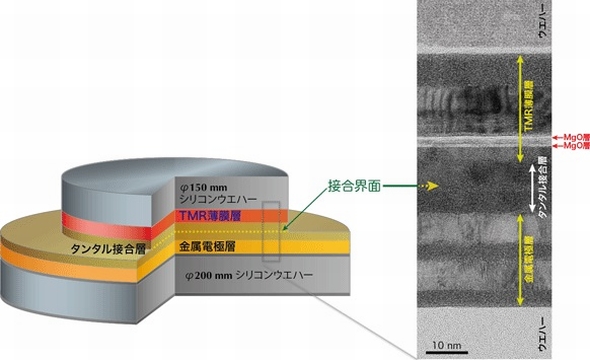

ウエハーダイレクト接合直後の試料断面を電子顕微鏡で確認した。この画像から接合界面部分が完全に連続膜としてつながっており、欠陥や空隙も無く高品位のウエハー接合であることが分かった。なお、ウエハー接合後にMgOトンネル絶縁層が破壊することもなかったという。特に研究グループは、「TMR素子と相性が良いタンタルを用いて高品位の接合が行えたことは、MRAMを製造する上でとても重要」とみている。

Copyright © ITmedia, Inc. All Rights Reserved.