ニュース

MRAMの3次元積層プロセス技術を開発:大容量化と高性能化を可能に(2/2 ページ)

産業技術総合研究所(産総研)の薬師寺啓研究チーム長らは、不揮発性磁気メモリー「MRAM」の大容量化、高性能化につながる3次元積層プロセス技術を開発した。

5年以内には3次元積層MRAMの製品開発に着手へ

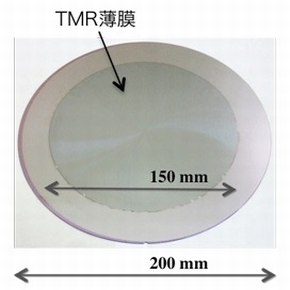

ウエハー裏面研削プロセスでは今回、研削と化学的エッチング技術を併用した。しかも機械的ダメージがTMR薄膜層に及ばないように加工条件を工夫した。これによって、TMR薄膜層を残しながら、ウエハーを完全に除去することができた。

研究グループは、開発した3次元積層プロセスを用い、サイズが28〜65nmのMRAMデバイスを作製し、動作を確認した。この結果、読み出しや書き込みの性能は劣化しないことが分かった。STT-MRAMの性能指標となるデータ書き込み効率は「2」となった。ウエハー接合時の圧着荷重やウエハー裏面研磨時の摩擦など、さまざまなダメージ要因についても、MRAM動作には影響しないことが分かった。

今回の研究では多結晶TMR薄膜を用いたが、機械的強度は単結晶TMR薄膜が強い。このため、今回開発した3次元積層プロセスを、そのまま単結晶TMR薄膜にも適用できるとみている。原子レベルでの薄膜平たん性や薄膜均質化による性能バラツキの排除、高性能な単結晶材料の使用などから、単結晶TMR薄膜を用いるメリットは大きいという。

研究グループでは今後、2年以内に単結晶TMR薄膜とCMOSウエハーの3次元積層プロセスを確立し、5年以内をめどに3次元積層MRAMの製品開発に着手する予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

伸縮性導体、5倍に伸ばしても高い導電率を実現

伸縮性導体、5倍に伸ばしても高い導電率を実現

東京大学の松久直司博士と染谷隆夫教授を中心とした研究チームは、長さを元の5倍に伸ばしても導電率が935S/cmという世界最高レベルを示す伸縮性導体の開発に成功した。 名古屋大、カーボンナノベルトの合成に成功

名古屋大、カーボンナノベルトの合成に成功

名古屋大学は、カーボンナノチューブの筒状構造を持つ炭素分子「カーボンナノベルト」の合成に初めて成功した。 首都大学東京、導電性ポリマーの精密合成法開発

首都大学東京、導電性ポリマーの精密合成法開発

首都大学東京の野村琴広氏らは、優れた光機能を発現するπ共役ポリマーの精密な合成法を開発した。 蓄電容量はLi電池の15倍、NIMSのリチウム空気電池

蓄電容量はLi電池の15倍、NIMSのリチウム空気電池

物質・材料研究機構(NIMS)は、蓄電容量が極めて高いリチウム空気電池を開発した。従来のリチウムイオン電池(Li電池)に比べて15倍に相当する高さで、EV(電気自動車)の走行距離をガソリン車並みに延ばすことも可能となる。 「光子1個が見える」、産総研が光子顕微鏡を開発

「光子1個が見える」、産総研が光子顕微鏡を開発

産業技術総合研究所(産総研)は、光子を1個ずつ観測できる「光子顕微鏡」を開発した。 産総研、「世界最高」の磁場中臨界電流密度実現

産総研、「世界最高」の磁場中臨界電流密度実現

産業技術総合研究所(産総研)は成蹊大学などと共同で、低コストの高温超電導線材を用いて、世界最高水準の磁場中臨界電流密度を実現した。