連載

究極の高密度不揮発性メモリを狙う強誘電体トランジスタ:福田昭のストレージ通信(73) 強誘電体メモリの再発見(17)(1/2 ページ)

今回は、1個のトランジスタだけでメモリセルを構成できる「FeFET(Ferroelectric FET)」または「強誘電体トランジスタ」について解説する。FeFETは、構造はシンプルだが、トランジスタの設計はかなり複雑になる。

強誘電体を電界効果トランジスタのゲート絶縁膜に導入する

本シリーズの第17回(前々回)では、強誘電体を使ったメモリセルの構造について簡単に説明した。1つはDRAMと似た構造のセルで、1個のトランジスタと1個の強誘電体キャパシターで構成する。トランジスタがセル選択素子、強誘電体キャパシターが記憶素子、という役割り分担になる。

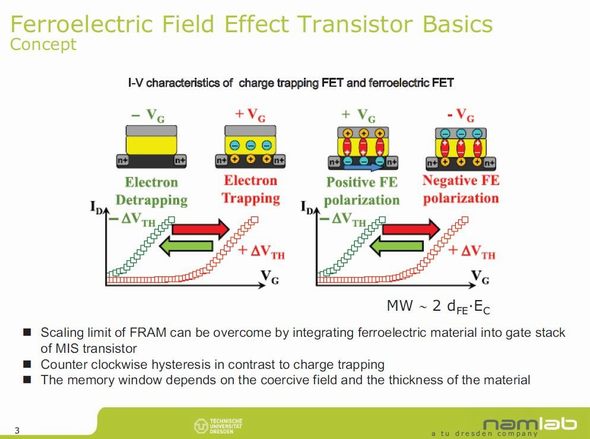

もう1つは電荷捕獲(チャージトラップ)方式フラッシュメモリと似た構造のセルで、MOSトランジスタ(MOSFET)のゲート絶縁膜を強誘電体にすることで、1個のトランジスタだけでメモリセルを構成する。強誘電体ゲート絶縁膜のトランジスタ(FET)が、セル選択素子と記憶素子の両方を兼ねる。このようなトランジスタを「FeFET(Ferroelectric FET)」「強誘電体トランジスタ」などと呼んでいる。1個のトランジスタだけでメモリセルを構成できるので、究極ともいえる、高密度なメモリを原理的には実現可能だ。

1個のトランジスタがセル選択素子と記憶素子を兼ねるメモリセルとその動作。左半分は、電荷捕獲(チャージトラップ)方式フラッシュメモリのトランジスタと電流電圧特性。ゲート絶縁膜の捕獲準位が電子を蓄積することで、トランジスタのしきい電圧(VTH)がシフトする。右半分は、強誘電体をゲート絶縁膜に採用したトランジスタ(強誘電体トランジスタ(FeFET))と電流電圧特性。強誘電体ゲート絶縁膜の分極の方向が変化することで、トランジスタのしきい電圧(VTH)がシフトする。いずれのトランジスタも、電源を切ってもしきい電圧の位置は動かない。出典:NaMLabおよびドレスデン工科大学(クリックで拡大)

Copyright © ITmedia, Inc. All Rights Reserved.