連載

究極の高密度不揮発性メモリを狙う強誘電体トランジスタ:福田昭のストレージ通信(73) 強誘電体メモリの再発見(17)(2/2 ページ)

今回は、1個のトランジスタだけでメモリセルを構成できる「FeFET(Ferroelectric FET)」または「強誘電体トランジスタ」について解説する。FeFETは、構造はシンプルだが、トランジスタの設計はかなり複雑になる。

メモリ特性とスイッチング特性の両方を考慮

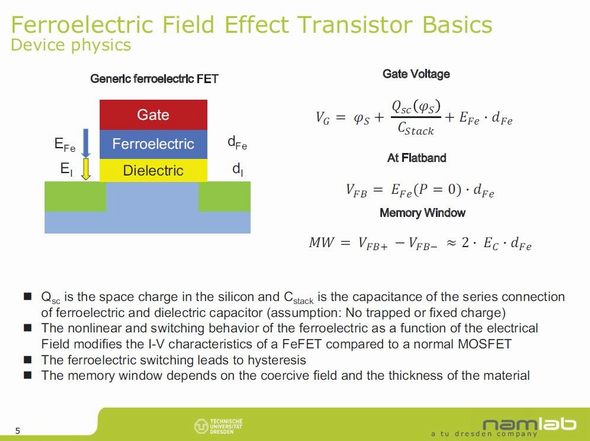

「FeFET(Ferroelectric FET)」あるいは「強誘電体トランジスタ」の基本的な構造は、かなりシンプルである。シリコン基板(シリコンウエハー)の表面には、常誘電体の薄いゲート絶縁膜が載る。その上に、強誘電体の絶縁膜が載り、最上層はゲート電極となる。普通のMOSFETとの違いは、ゲート絶縁膜が2層構造になっただけ、ともいえる。

ただしトランジスタの設計はかなり複雑だ。普通のMOSFETはスイッチあるいはアンプであり、メモリではない。しかし強誘電体トランジスタはメモリなので、スイッチング特性とメモリ特性の両方が関連する。ゲート電圧、ドレイン電流、ゲートスタックの静電容量、常誘電体膜中の電界、強誘電体膜中の電界、強誘電体のスイッチング特性(分極反転特性)、強誘電体の膜厚と抗電界などを考慮しなければならない。

例えばメモリウィンドウ(オン状態とオフ状態の差分)は、強誘電体の膜厚と抗電界の大きさに比例する。また書き込みの速度は、スイッチング特性(分極特性)に依存する。

強誘電体トランジスタ(FeFET)の研究は、従来の強誘電体材料であるペロブスカイト系セラミックスと、強誘電性の有機高分子を使い、1990年代後半から活発になってきた。次回は、その歩みをご報告しよう。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

PCIeが今後の主流に

PCIeが今後の主流に

今回から始まるシリーズでは、SSDインタフェースの最新動向に焦点を当てて解説する。SSD関連のインタフェースは数多く存在するが、近年、採用が進んでいるのがPCIeだ。 NVIDIAがエネルギー効率の高い相互接続技術を解説(前編)

NVIDIAがエネルギー効率の高い相互接続技術を解説(前編)

バスやリンクなどの相互接続(インターコネクト)は大きなエネルギーを消費する。では、どのようにして消費電力を下げ、エネルギー効率を高めればよいのか。前編では、信号振幅を小さくする方法と、電荷を再利用する方法の2つについて解説する。 メモリ価格の高騰はしばらく続く

メモリ価格の高騰はしばらく続く

DRAMとNAND型フラッシュメモリは価格は上昇していて、この傾向は今後もしばらく続くという。 東芝メモリの売却先はまだ決まらず

東芝メモリの売却先はまだ決まらず

東芝は、東芝メモリについて「2017年8月31日の取締役会で売却先を決定」とする一部の報道を否定し、「開示すべき決定事項はない」として、売却先がまだ決定していないことを明らかにした。 東芝がQLCの3D NANDを試作、96層プロセスの開発も

東芝がQLCの3D NANDを試作、96層プロセスの開発も

東芝メモリは、同社の3D NAND型フラッシュメモリ「BiCS FLASH」について、4ビット/セル(QLC)技術を用いた試作品と、96層積層プロセスを用いた試作品を開発し、基本性能を確認したと発表した。 2017年の世界半導体市場、WSTSが上方修正

2017年の世界半導体市場、WSTSが上方修正

世界半導体市場統計(WSTS)は、2017年第2四半期の半導体市場の実績値に基づき、2017年の同市場の予測を更新した。2016年比で11.5%増としていた見通しを、17%増に上方修正している。