「不揮発性DRAM」へのアプローチ(後編):福田昭のストレージ通信(85) 反強誘電体が起爆するDRAM革命(6)

後編では、NaMLabやドレスデン工科大学などの共同研究グループが試作した、3次元構造の反強誘電体キャパシターアレイと、その特性を紹介する。

DRAM製品と同様の3次元セルキャパシターを作製

前編では、DRAM製品のセルキャパシターに採用されている絶縁材料が偶然にも、反強誘電体と同じ「二酸化ジルコニウム(ZrO2)」であるという事実を明らかにした。そしてDRAMキャパシターと同様の絶縁膜である3層構造(ZAZ(ZrO2/Al2O3/ZrO2)構造)を試作し、残留分極を持たせられること、すなわち、不揮発性メモリを具現化可能なことを示した。

ただし、前編で示した試作結果は、平面状(プレーナタイプ)のキャパシターを作製した結果である。DRAM製品のセルキャパシターは、細長い円筒のような3次元構造を採用することで、シリコン面積当たりの静電容量(充電電荷量)を稼いでいる。

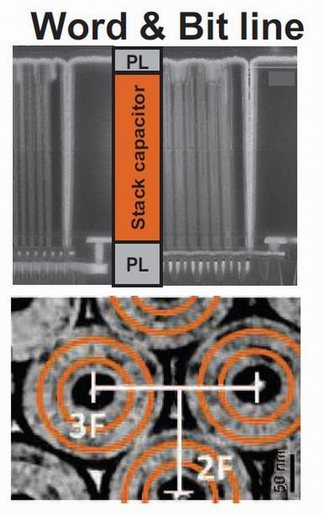

そこでNaMLabやドレスデン工科大学などの共同研究グループは、46nm世代のDRAM製造プロセス(4Gビットのシリコンダイに相当)を利用して細長い円筒のような3次元構造の反強誘電体キャパシターアレイを試作し、特性を確認することにした。

試作した3次元キャパシターアレイの断面観察像(上:走査型電子顕微鏡)と上面観察像(下:透過型電子顕微鏡)。ZAZ構造の厚みは7.5nm、円筒状キャパシターのアスペクト比は30(水平方向を1とすると、垂直方向の長さが30)である。出典:NaMLabやドレスデン工科大学などの共同研究グループが2016年12月に国際学会IEDMで発表した資料から(クリックで拡大)

3次元キャパシターで残留分極の存在と1000万回の書き換えを確認

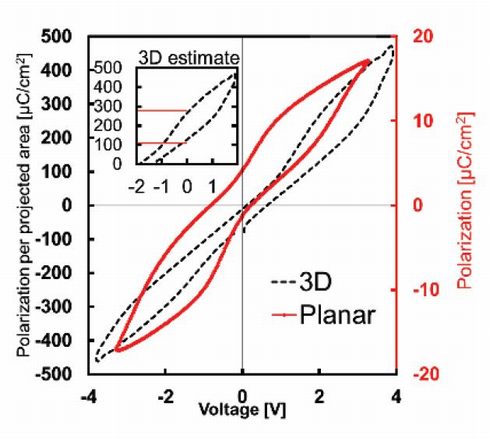

その結果、シリコン面積当たりでプレーナタイプの30倍前後と大きな残留分極電荷を、3次元構造のキャパシターで得ることができた。試作した円筒状キャパシターのアスペクト比が30なので、プレーナタイプでの品質を維持できていることが分かる。

プレーナタイプのキャパシターにおける分極特性(赤線、右の縦軸)と3次元構造のキャパシターにおける分極特性(黒い点線、左の縦軸)。出典:NaMLabやドレスデン工科大学などの共同研究グループが2016年12月に国際学会IEDMで発表した資料から(クリックで拡大)

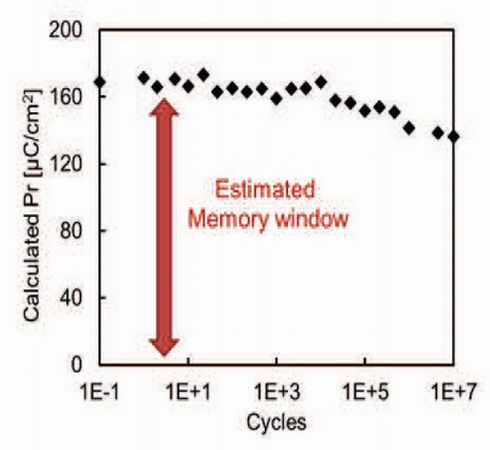

さらに、試作した3次元キャパシターで、強誘電体メモリと同様の書き換えを繰り返してみた。1000万回の書き換えサイクルを経ても、十分な読み出しマージンがあることを確認した。

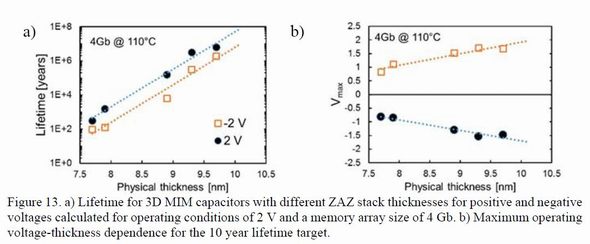

データ保持特性も展望は明るい。計算によると、110℃と比較的高い温度にもかかわらず、絶縁膜厚と動作電圧の最適化によって10年以上のデータ保持期間を達成できる見通しを得ている。

試作した3次元キャパシターのデータ保持特性(計算値)。左はZAZ構造の厚みと動作電圧の関係。8nm前後の厚みがあれば、100年以上のデータ保持期間を実現できる。右は10年間のデータ保持期間を達成可能な厚みと最大動作電圧の関係。膜厚が8.5nm、最大動作電圧が±1.5Vの条件で、10年のデータ保持期間を達成できる。出典:NaMLabやドレスデン工科大学などの共同研究グループが2016年12月に国際学会IEDMで発表した資料から(クリックで拡大)

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

反強誘電体とは何か

反強誘電体とは何か

強誘電体の新材料である二酸化ハフニウムは、実は条件次第では「反強誘電体(Antiferroelectrics)」になる。今回から、この反強誘電体を不揮発性メモリに応用する研究について解説していこう。 東芝、四日市第6製造棟への投資を前倒し

東芝、四日市第6製造棟への投資を前倒し

東芝は、東芝メモリ四日市工場第6製造棟への投資計画を前倒しし、2018年3月期中に実施する投資規模を1100億円増額すると発表した。 次世代半導体材料、2023年に153億円規模へ

次世代半導体材料、2023年に153億円規模へ

SiC(炭化ケイ素)などワイドバンドギャップ半導体単結晶の国内市場(メーカー出荷金額)は、2017年の約96億円に対し、2023年は約153億円に拡大する見通しとなった。 iPhone 8の分解で垣間見た、Appleの執念

iPhone 8の分解で垣間見た、Appleの執念

2017年9月に発売されたApple「iPhone 8」。iPhone 8の分解から見えたのは、半導体設計に対するAppleの執念だった。 誰も知らない「生産性向上」の正体 〜“人間抜き”でも経済は成長?

誰も知らない「生産性向上」の正体 〜“人間抜き”でも経済は成長?

「働き方改革」に関連する言葉で、最もよく聞かれる、もしくは最も声高に叫ばれているものが「生産性の向上」ではないでしょうか。他国と比較し、「生産性」の低さを嘆かれる日本――。ですが、本当のところ、「生産性」とは一体何なのでしょうか。 AR/VR市場、2021年には2150億ドル規模に

AR/VR市場、2021年には2150億ドル規模に

IDC Japanは、AR(拡張現実)/VR(仮想現実)関連の世界市場予測を発表した。2017年の114億米ドルに対して、2021年は約2150億米ドルの市場規模に達する見通しである。日本市場は年率60%以上の成長を続けるが、世界への追い上げが課題になるという。