モノリシック3D IC、将来有望ながら課題は山積:実用化に近いデモもない?(1/2 ページ)

半導体チップの高速化や小型化を実現する技術として研究開発が続けられているモノリシック3D(3次元) ICだが、数多くの難しい課題が残っているようだ。

課題が山積するモノリシック3D IC

「モノリシック3D(M3D)技術は、半導体チップの高速化と低価格化、小型化を実現していくための手法として、非常に有望視されている。しかし、ここ数四半期にわたって注目を集めてきたものの、関連する多くの取り組みがまだ研究段階にあることから、技術の向上とエコシステムの構築を実現するには、まだ数々の問題が山積している」

これは、米国カリフォルニア州サンフランシスコで2017年10月16〜19日に開催された年次イベント「IEEE S3Sカンファレンス」において提示された見解である。同イベントでは、ARMやCEA-Leti(フランス原子力庁の電子情報技術研究所)、DARPA(米国防高等研究計画局)、Mentor Graphics、Qualcommなどが、M3D分野における取り組みについて発表を行った。

M3Dは、1つ以上のダイの上に垂直に積層したブロックに、さまざまな機能を搭載することを目標としているが、そのほとんどの手法において、まだ実用化に向けたデモを披露するには至っていない状況にある。

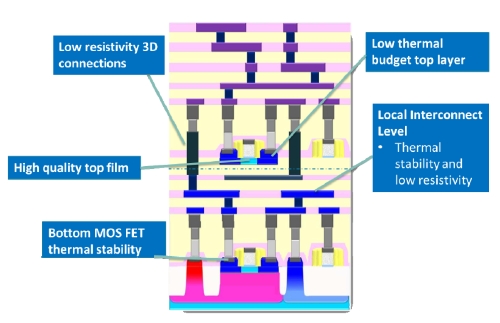

CEA-Letiは過去数年間にわたり、垂直積層トランジスタ技術「Cool Cube」の開発に取り組んできた。CEA-Letiのパートナー企業として、IBMやQualcomm、STMicroelectronicsなどが、Cool Cubeの開発に携わっている。Cool Cubeは、有望な技術として期待されてきたが、完全なM3Dチップにおけるグローバルルーティングなどの問題に対応するための方法を、まだ提示できていない。

今回、Qualcommのリサーチディレクターが、Cool Cubeに関する半日のプログラムを共催している。同氏は現在も、既存手法の数多くの欠点について精力的に調査を行っており、3D VLSI分野に対する強い熱意を示す。

Qualcommは何年か前に、TSV(Through Silicon Via:シリコン貫通ビア)の研究開発にも熱心に取り組んでいた。このTSVは、モバイルアプリケーションプロセッサに適用することができると考えられていた。しかしQualcommは、TSVの温度とコストの問題をほとんど解決することができず、現在ではこの取り組みを中止してしまっている。一方で、TSMCをはじめとするさまざまな企業が、ウエハーレベルのファンアウトパッケージング(FOWLP:Fan Out Wafer Level Packaging)技術の開発を進めている。TSMCの同技術は、Apple「iPhone」のプロセッサに採用されている。

DARPAも期待する技術だが……

新興企業であるMonolithIC 3Dは、半導体分野のベテラン専門家であり同社のCEO(最高経営責任者)を務めるZvi Or-Bach氏の指揮の下、M3Dを推進してきた。同氏は、今回のイベントの主催者を務めている。MonolithIC 3Dの全従業員は5人で、Or-Bach氏だけがフルタイムの社員だという。同社は、M3D関連の強力なアイデアとIP(Intellectual Property)を保有しているものの、シリコン上で試験を行うためのパートナー企業を、まだ見つけることができないという。

DARPAは、「M3Dは、半導体業界において利益が低迷し、コストが上昇していく中でも、再び業界を活性化させることが可能な、数々の有望な取り組みの中の1つである」と考えているようだ。DARPAは、次世代半導体開発関連の6つのプログラムの中の1つとして、チップスタックの研究開発を進めていく予定で、一部の企業からM3Dプロジェクトに関する提案を受けているという。

米国の半導体市場調査会社であるInsight64で主席アナリストを務めるNathan Brookwood氏は、「例えるなら、建物の中の同じフロアの端から端までを進むのではなく、階段を上り下りしているような状況だといえるだろう。チップ上でキャッシュから演算器までの間を数十ミリメートル進むのではなく、ほんの1〜2mmしか前進することができないような状態だ」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.