IoTでは50セントのチップを実現する技術が必要だ:ARM TechConで技術者らが主張(1/2 ページ)

IoT向けに使われるSoC(System on Chip)は、50米セント以下で実現できるようにする必要がある――。「ARM TechCon 2017」では、技術者らがそのような議論を行った。

50米セント以下のSoCが求められる

2017年10月24〜26日に米カリフォルニア州サンタクララで開催されたARMの技術者向けイベント「ARM TechCon 2017」のパネルディスカッションでは、IoT(モノのインターネット)の未来は、50米セント以下のチップによって決まる可能性が示唆された。IoTで求められるチップサイズに小型化するには、SoC(System on Chip)に新しいメモリ技術や接続技術、センサーが必要になるが、実現への道はまだ確立されていない。

パネリストらによると、「現在のSRAMやフラッシュメモリ、Bluetoothインタフェース、センサーは消費電力が大きすぎて、2027年までに大幅な増加が予想されるIoTノードに対応できない」という。同パネルディスカッションでは、これらに代わるいくつかのソリューションについて説明された。

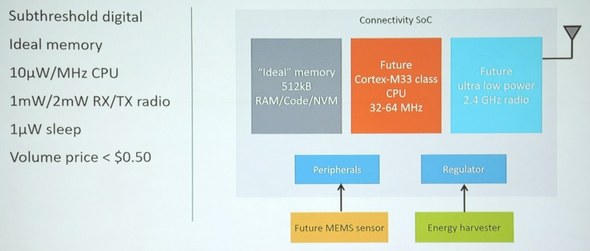

ARMのワイヤレスグループでソフトウェア担当ディレクタを務めるJason Hillyard氏は、「2027年には、エンドノードSoCの消費電力が10μW/MHzに抑えられ、1〜2mWの電力でデータを無線で送受信できることが望ましい」と述べている。同氏の提唱する「slideware SoC」は、環境発電に適したサブスレッショルド回路で構築した新しいアーキテクチャを採用するという。

適切なメモリ技術がない

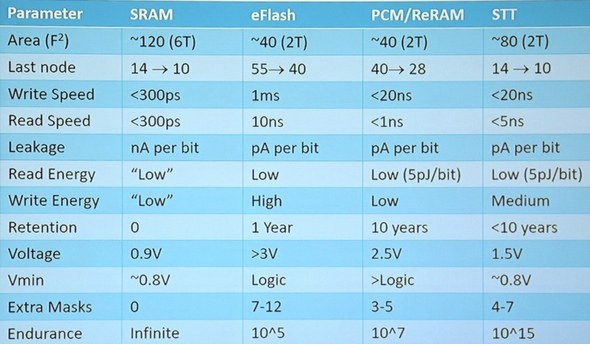

ARMの上級主席リサーチエンジニアを務めるLucian Shifren氏は、「このようなデバイスを実現する上で最大の問題の1つは、適切なメモリがないことだ」と指摘する。

Shifren氏は、「メモリの消費電力は今後の主要課題だ。ReRAM(抵抗変化メモリ)とSTT-RAM(スピン注入メモリ)は、SRAMとフラッシュメモリに代わるソリューションとして期待されているが、どちらもう現時点ではうまく機能するとは思えない。STT-RAMは高額で書き込み時の消費電力が大きすぎる点、ReRAMと相変化メモリは高い電圧を使用する点がネックとなって、現実的な代替ソリューションとはいえない」と述べている。

ARMの主席技術者を務めるMike Muller氏は、EE Timesとのインタビューの中で、「当社は、学術研究に基づいた新しいメモリを使ってテストチップを開発した」と語った。ただし、同氏は、テストチップの技術詳細については明らかにしていない。

Muller氏は、「最終的な目標は、メモリだけでなく論理回路にも有用な、不揮発性で低消費電力の設計を実現することだ。それまでは、フラッシュメモリの代替技術となることは難しいだろう」と述べている。

米国のマイコンベンダーであるAmbiq MicroのCTO(最高技術責任者)を務めるScott Hanson氏は、「サブスレッショルド回路をベースにしたマイコンは既に、メモリの壁にぶつかっている。ローカルでたくさんのデータの書き込みを行いたいというユースケースがあるが、現在は対応できない」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.