IEDM 2017の講演2日目(12月5日)午後(その1):記憶密度を2倍に高める3D NAND技術:福田昭のデバイス通信(121) 12月開催予定のIEDM 2017をプレビュー(5)(1/2 ページ)

今回から、12月5日午後の注目講演を順次紹介していく。電荷ベースのメモリ、最先端CMOSのさらなる微細化手法、最先端の金属ゲート技術やコンタクト技術など、興味深いテーマが並ぶ。

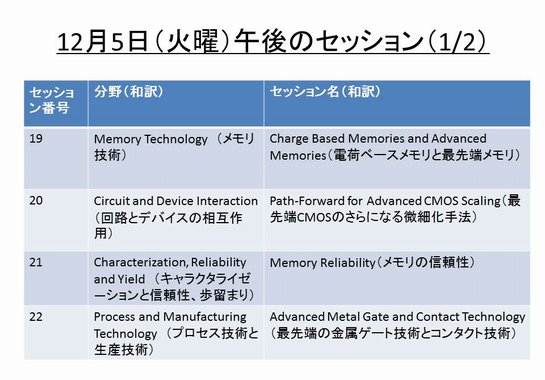

12月5日午後のセッション19からセッション22までを概観

前回は、技術講演の2日目である12月5日(火曜日)の午前の講演セッションと注目講演をご報告した。今回は、同日の午後のセッションから、概要と注目講演をご紹介する。

この時間帯は、セッション19からセッション26までの8本の講演セッションが同時並行で進む。今回はその中で、セッション19からセッション22までの概要をお知らせしよう。テーマは、電荷ベースメモリと最先端メモリ(セッション19)、最先端CMOSのさらなる微細化手法(セッション20)、メモリの信頼性(セッション21)、最先端の金属ゲート技術とコンタクト技術(セッション22)である。

低電圧、高速動作の強誘電体トランジスタ技術

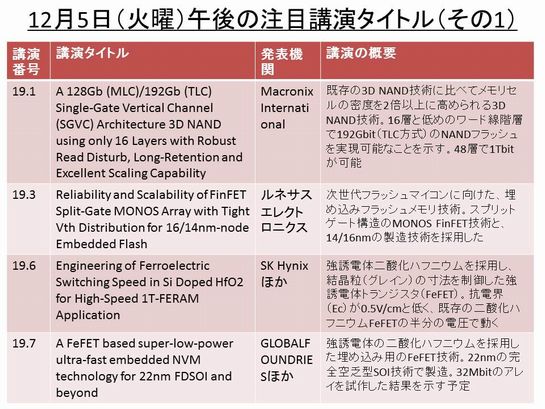

午前中に負けず、午後のセッションも注目すべき講演が少なくない。まずセッション19では、最先端のメモリ技術が続出する。

Macronix Internationalは、既存の3D NAND技術に比べてメモリセルの密度を2倍以上に高められる3D NAND技術を開発した(講演番号19.1)。16層と少なめのワード線階層で192Gビット(TLC方式)のNANDフラッシュメモリを実現できることを示す。48層で1Tビットが可能だとする。

ルネサス エレクトロニクスは、同社の次世代フラッシュマイコン(フラッシュメモリを内蔵するマイクロコントローラ)に向けた、埋め込みフラッシュメモリ技術を発表する(講演番号19.3)。スプリットゲート構造のMONOS FinFET技術で、14/16nmの製造技術を採用した。データ保持期間のテスト後も、しきい電圧のばらつきを抑えられているとする。

SK HynixとLam Researchなどの共同研究グループは、強誘電体の二酸化ハフニウムを採用し、結晶粒(グレイン)の寸法を制御した強誘電体トランジスタ(FeFET)を試作した(講演番号12.6)。1個のトランジスタが不揮発性メモリセルとして機能する。抗電界(Ec)が0.5V/cmと低く、既存の二酸化ハフニウムFeFETの半分の電圧で動く。またスイッチング速度が3倍に向上した。

GLOBALFOUNDRIESとNaMLabなどの共同研究グループは、強誘電体の二酸化ハフニウムを採用した、埋め込み用の強誘電体トランジスタ(FeFET)技術を発表する(講演番号12.7)。22nmの完全空乏型SOI(FD SOI)技術で製造する。32Mビットのトランジスタアレイを試作した結果を示す予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.