「RISC-V」はEmbeddedでマーケットシェアを握れるのか:RISC-V Day 2017 Tokyo(4/5 ページ)

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。

RISC-Vを商用化するSiFive

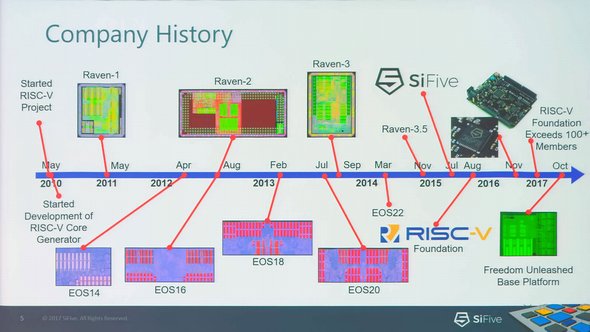

3つ目はSiFiveのJack Kang氏によるセッションである。SiFiveは、いわばRISC-Vを商用化するための会社であり、「E31」「E51」「U54-MC」という3種類のIPを提供する他、「Freedom SoC」と呼ばれるこのIPを実装したSoC、さらには、このFreedom SoCを搭載した「HiFive 1」という開発ボードの提供も開始している(写真21)。

写真21:もともとのRaven ProjectからそのままRISC-Vの開発にシフトしたメンバーがそのままSiFiveに在籍して開発を行っていることもあって、Company HistoryがRaven-1から始まっているのは、さすがである(クリックで拡大)

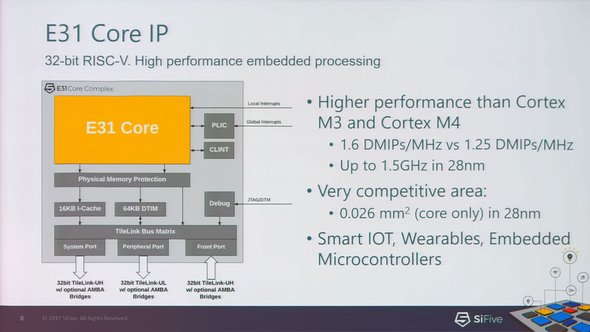

さてそのSiFive、EシリーズがEmbedded MCU向け、Uシリーズがアプリケーションプロセッサ向けという扱いで、なのでEシリーズは仮想記憶のサポートもなくMPU(Memory Protection Unit)のみ、一方のUシリーズは仮想記憶やMMUのサポートありといった違いがある。最小構成のE31 Core(写真22)は、それでもターゲットはCortex-M3/M4クラスを狙っているのが分かる。

写真22:足回りは独自のTileLinkである。TileLinkの説明は、「FPGA開発日記」著者の@msyksphinz氏(氏も「RISC-Vオープンソースハードウェア概説」という講演を行っており、これもまた大変に面白かった)の2017年7月13日の記事が分かりやすいと思う(クリックで拡大)

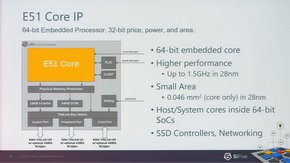

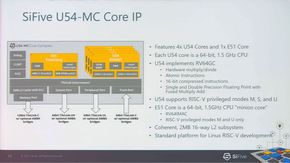

E51 Coreはさらに高性能な、しかも64bitのコアである(写真23)。これに対してU54-MCは、Quad U54+E51というマルチコア構成のIPである(写真24)。こちらは本当にアプリケーション向けプロセッサで、性能的に言えば例えば(MACOMの買収後に別ファンドに売っ払われて、ついに最近サイトのアクセスまでできなくなってしまった)旧Applied MicroのX-Geneとかに近い感じである。

左=写真23:性能ターゲットはCortex-M7クラスに相当するように思われる。あるいはCortex-A5クラスか。SSD ControllerとかNetworkingといえばそのあたりだろう/右=写真24:別にbig.LITTLE的な動作ではなく、U54がアプリケーション処理、E51がI/O管理といった使い方を想定していると思われる(クリックで拡大)

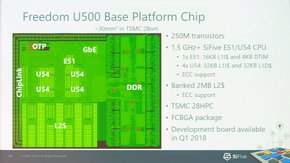

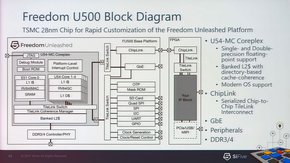

左=写真23:性能ターゲットはCortex-M7クラスに相当するように思われる。あるいはCortex-A5クラスか。SSD ControllerとかNetworkingといえばそのあたりだろう/右=写真24:別にbig.LITTLE的な動作ではなく、U54がアプリケーション処理、E51がI/O管理といった使い方を想定していると思われる(クリックで拡大)このU54-MCにメモリコントローラーや周辺I/Oを組み込んだFreedom U500のダイサイズが30mm2というのは、かなりコスト競争力のありそうな構成である。Armで言えば、Cortex-A53×1〜2coreのSoCと競合という感じになるのではないかと思われる(写真25)。内部構造はこんな感じ(写真26)で、ChipLink経由でFPGAなどを使ってまず自分のIPを実装して検証を行い、うまくいく様ならIPをSiFiveから購入、自分のIPも組み込んでSoCを開発する、といったシナリオを考えているようである。

Copyright © ITmedia, Inc. All Rights Reserved.