EUV、5nm付近でランダム欠陥 imecが報告:レジストにも課題が(1/2 ページ)

EUV(極端紫外線)リソグラフィの5nmプロセスで、ランダム欠陥が発生することを、imecの研究者が報告した。

5nm付近でランダム欠陥が発生

EUV(極端紫外線)リソグラフィの5nmプロセスで、ランダム欠陥が発生する現象が報告された。この問題を回避すべくさまざまな技術を適用しているが、これまでのところ、明確な解決策は見つかっていないという。

GLOBALFOUNDRIESやSamsung Electronics、TSMCは、2018年の7nmチップの製造に向けて、250Wの光源を使用してEUVシステムの有用性を最大限まで高めることを競い合っている。このニュースは、こうした状況の中で報じられた。このランダム欠陥の発生によって、半導体製造におけるコストの増加と複雑化を解消する万全の策は存在しないということがはっきりと示された。

ベルギーの研究開発機関imecのパターニングエキスパートであるGreg McIntyre氏は、米国カリフォルニア州サンノゼで2018年2月25日〜3月1日に開催された半導体リソグラフィ技術の国際会議「SPIE Advanced Lithography 2018」の講演で、「ファウンドリー各社は最新のEUVスキャナーの導入によって7nmチップの実現を目指している。ただし、微細な線幅と正孔(ホール)を形成できるのかは不明だ」と語った。

McIntyre氏のように楽観な見通しを持つ人は、いわゆる“確率的影響”の解決策が登場すると確信しているようだ。一方、懐疑派は、今回の欠陥が報告されたことで、開発が(予定よりも)遅れている高コストなEUVシステムが、半導体製造の主流装置になる可能性について、さらに疑いを強めている。

Intelの元リソグラフィ技術者であるYan Borodovsky氏は、SPIE Advanced Lithography 2018の基調講演で、「EUVステッパーで2〜3回露光することで、5nmチップ、さらには3nmチップも実現できるだろう」と語った。

報告された不具合は、15nm付近で突然発生するという。15nmプロセスは、5nmチップを目指す上で必要となるプロセス技術である。EUV装置メーカーであるASMLは2017年、「SPIE Advanced Lithography 2017」(米国カリフォルニア州サンノゼ、2017年2月26日〜3月2日)で、「より微細なプロセス向けの次世代EUVシステムの準備を進めているが、実用化は2024年ごろになる見通しだ」と述べている。

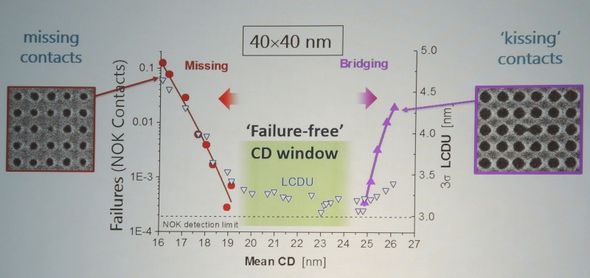

今回報告されたランダム欠陥は、さまざまなパターンがあるという。具体的には、不完全なホールが形成される、ラインに亀裂が生じる、何らかの欠損によって2本の線または2つのホールが接触するといったパターンがある。非常に微細であるため、研究者がこうした不具合を発見するのに数日を要する場合もあるという。

ある研究者は、欠陥の発見や除外に向けた取り組みとして、ラインの粗さを測定する標準的な手法を提案する予定だという。McIntyre氏は、「同手法は、欠陥の解明の鍵になると期待される」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.