電源モジュールを小型、高効率化するパッケージ技術:GaNやSiCの長所をさらに生かす

太陽誘電は「TECHNO-FRONTIER 2018(テクノフロンティア)」(2018年4月18〜20日、幕張メッセ)で、パッケージ技術「Power Overlay(POL)」を紹介した。

太陽誘電は「TECHNO-FRONTIER 2018(テクノフロンティア)」(2018年4月18〜20日、幕張メッセ)で、GaN(窒化ガリウム)やSiC(炭化ケイ素)を用いた電源モジュールに理想的なパッケージ技術として「Power Overlay(POL)」を紹介した。

ワイヤボンディングを排し、銅メッキで素子同士を相互接続

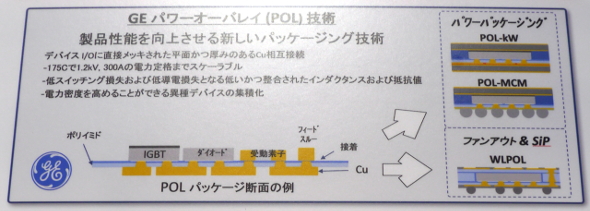

POLは米GEが開発したパッケージング技術で、太陽誘電は2014年末にGEベンチャーズから知的財産をライセンスされ共同開発を行ってきた(関連記事:太陽誘電とGEが電子部品内蔵技術で協業)。

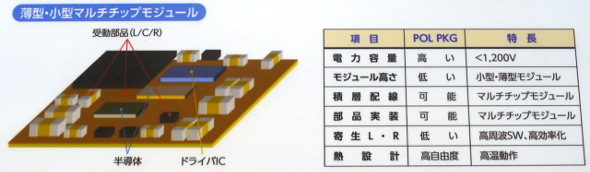

POLでは、パワー素子やドライバ、その他受動部品はポリイミドフィルム上に接着される。素子が接着されたフィルムの下部よりボンディング位置にレーザー光を照射し、フィルムに貫通穴を設け、その穴に銅メッキを流し込むことで素子同士を相互接続するという技術だ。

ワイヤボンディングによるパッケージと比較して素子同士の設置間隔を狭められるため、配線長削減により寄生インダクタンスなど寄生成分の低下が可能だ。これにより、スイッチング高周波化と小型受同部品の採用に貢献し、モジュールの高効率化と小型化の両立を実現する。実装高さも抑えられるため、パワー素子に直接ヒートシンクを設置するなど熱設計の自由度も高められるという。

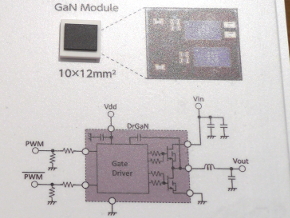

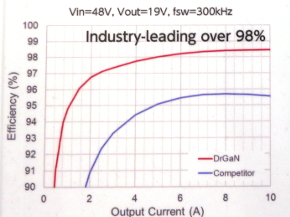

同社ブースでは、GaNハーフブリッジモジュールを展示。モジュールは10×12mmサイズで、GaN FETとドライバ、受動部品をPOLを用いて1チップ化。48V入力、19V出力でスイッチング周波数300kHz条件により動作させた場合、最大で98%超の変換効率を提供するとし、競合品と比較して2%の効率向上を達成したという。

POLは「数年以内の商用化を目指す」(同社担当者)とし、想定する利用領域にIT機器、産業機械とロボット、自動車を挙げる。同社担当者は「(同領域で活用が進む)GaN/SiCパワーデバイスのさらなる小型、高効率化に貢献する」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

GE POL用いたパワーモジュール、効率10%向上へ

GE POL用いたパワーモジュール、効率10%向上へ

太陽誘電は、2016年10月4〜7日に幕張メッセで開催された「CEATEC JAPAN 2016」で、研究開発中のGE POL(Power OverLay)パッケージ技術を用いたパワーモジュールの展示を行った。 太陽誘電とGEが電子部品内蔵技術で協業

太陽誘電とGEが電子部品内蔵技術で協業

太陽誘電とGEベンチャーズの両社は2016年7月、2014年末から半導体パッケージ基板などに応用可能なワイヤボンド不要の電子部品内蔵基板技術分野で協業していることを明らかにした。 モバイル端末向けの最先端パッケージング技術

モバイル端末向けの最先端パッケージング技術

今回から、モバイル端末向けのパッケージング技術について解説する。大きく分けて、ウエハーレベルのファンアウトパッケージング(FOWLP)、パネルレベルのファンアウトパッケージング(FOPLP)、プリント基板へ回路素子を埋め込むパッケージング(ESP)がある。まずは、パッケージング技術における「ファンアウト」の意味を確認しつつ、Infineon Technologiesが開発した“元祖FOWLP”を説明したい。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 パッケージングとEDAの技術革新が必要 AMDのCTO

パッケージングとEDAの技術革新が必要 AMDのCTO

AMDは現在、7nmプロセスの実用化に向けて開発を加速している。同社の製品のうち、7nmプロセスを最初に適用するプロセッサは「Zen 2」「Zen 3」の予定だ。AMDのCTOを務めるMark Papermaster氏は、プロセスの微細化や、「ムーアの法則プラス」の時代では、パッケージング技術とEDAツールにおける技術革新が必要になると話す。 Hot Chips 2017、チップ積層技術に注目集まる

Hot Chips 2017、チップ積層技術に注目集まる

米国カリフォルニア州クパチーノで2017年8月20〜22日に開催された「Hot Chips 2017(Host Chips 29)」では、パッケージング技術やインターコネクト技術などを含め、特に2.5D(2.5次元)のチップ積層技術に注目が集まった。