微細化限界に達したフラッシュをMRAMで置き換え:福田昭のストレージ通信(102) GFが語る埋め込みメモリと埋め込みMRAM(2)(1/2 ページ)

埋め込みフラッシュメモリが直面する課題は、微細化の限界である。GLOBALFOUNDRIESは、2xnm以下の技術世代に向けた埋め込み不揮発性メモリとして、MRAM(磁気抵抗メモリ)を考えている。

高電圧回路とゲート絶縁膜がフラッシュの微細化を阻む

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。2017年12月に開催されたIEDMでは、「Memories for the future: device, technologies, and architecture(将来に向けたメモリデバイスの技術とアーキテクチャ)」と題したショートコースが開催された。このショートコースでは6本の技術講座が午前から午後にかけて実施された。

その中から、埋め込みメモリ技術(CMOSロジックとメモリを同じシリコンダイに混載する技術)に関する講座「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」が興味深かったので、その概要を前回からシリーズでお届けしている。講演者はシリコンファウンダリー(半導体製造請け負いサービス企業)大手のGLOBALFOUNDRIESでeNVMフェローをつとめるDanny P. Shum氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、SoC(System on Chip)やマイコンなどが埋め込むメモリの役割りと種類を概観した。大容量の埋め込み不揮発性メモリは、フラッシュメモリが主流となっている。ソフトウェア(ファームウェア)のプログラムコードを格納することが主な用途だ。

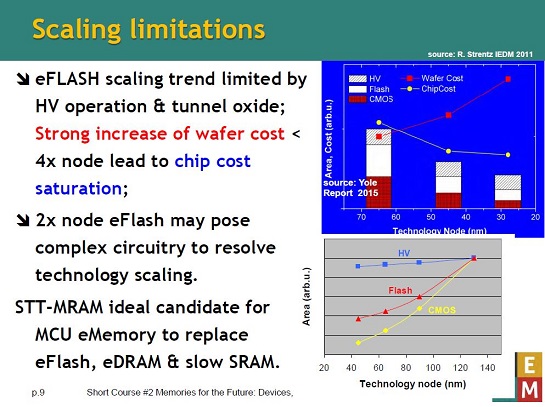

埋め込みフラッシュメモリが直面する課題は、微細化の限界である。4xnm世代から限界が無視できなくなり、2xnm世代では限界を突破する見込みがかなり低くなりつつある。

微細化を阻む技術的な課題はいくつかある。まず、フラッシュメモリがデータの書き込みと消去に高い電圧を必要とすることだ。微細化を進展させるためには、駆動電圧を下げなければならないのだが、フラッシュメモリでは原理的に、書き込み/消去の電圧を下げることが難しい。次に、埋め込みフラッシュメモリでは、ゲート絶縁膜をあまり薄くできない。微細化を進めるには、ゲート絶縁膜を薄くすることが求められる。しかしフラッシュメモリでゲート絶縁膜を薄くすると蓄積電荷が基板側に逃げてしまい、データを保持できないという問題が起こる。

従って2xnm世代では、CMOSロジックのトランジスタ回路に比べると、埋め込みフラッシュメモリのトランジスタ回路とメモリセルアレイは相対的に微細化が遅れ、大きなシリコン面積を占めるようになってきた。言い換えると、CMOSロジックを微細化しても、埋め込みフラッシュメモリの記憶密度が上がらないのだ。

そこでGLOBALFOUNDRIESでは、2xnm以下の技術世代に向けた大容量の埋め込み不揮発性メモリとして、MRAM(磁気抵抗メモリ)を考えている。電子スピンの注入によって磁化方向を変化させる、STT-MRAM技術がその最有力候補である。

埋め込みSTT-MRAMが置き換えるのは、埋め込みフラッシュメモリにとどまらない。将来は埋め込みDRAMと低速の埋め込みSRAMをSTT-MRAMで代替することをGLOBALFOUNDRIESは計画している。

Copyright © ITmedia, Inc. All Rights Reserved.