低電力で低コスト、FPGAを活用したAIスタック:ニューラルネットワークを最適化

Lattice Semiconductor(ラティス・セミコンダクター)は、極めて小さい電力消費と部材コストで、エッジ製品へのAI(人工知能)導入を行うことができる技術スタック「Lattice sensAI」を発表した。

Lattice Semiconductor(ラティス・セミコンダクター)は2018年5月25日、極めて小さい電力消費と部材コストで、エッジ製品側にAI(人工知能)機能を導入するための技術スタック「Lattice sensAI」を発表した。

さまざまなIoT機器へ機械学習を素早く導入

Lattice sensAIは、5つのスタックで構成されている。エッジコンピューティングにフォーカスした同社製FPGAを搭載した「ハードウェアプラットフォーム」、推論を行う「ニューラルネットワークIPコア」、機械学習ライブラリ「Caffe/TensorFlow」からFPGA用に変換するニューラルネットワークコンパイラなどの「開発ツール」、顔検出や速度標識検出などの「レファレンスデザイン」および、用途別に対応する「カスタム設計サービス」である。

ハードウェアプラットフォームとしては、「iCE40 UltraPlus FPGA」をベースに、イメージセンサーやマイク、ジャイロセンサーなどを搭載した「モバイル開発プラットフォーム(MDP)」と、「ECP5 FPGA」をベースにMIPI CSI-2やHDMI、GigE Visionといったインタフェース機能を搭載した「ビデオインタフェースプラットフォーム(VIP)」を用意した。

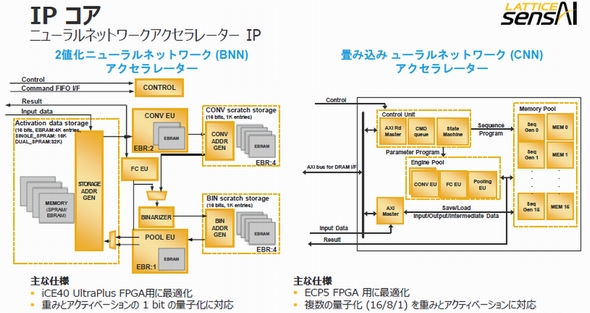

ニューラルネットワークIPコアは、iCE40 UltraPlus FPGA向けに最適化したバイナリーニューラルネットワーク(BNN)アクセラレーターと、ECP5 FPGA向けに最適化された畳み込みニューラルネットワーク(CNN)アクセラレーターを用意した。ちなみに、iCE40 UltraPlus FPGA向けBNN IPコアの実装には3000個のルックアップテーブルを用いるという。

ソフトウェア開発ツールとしては、ニューラルネットワークコンパイラツールと、設計ソフトウェアである「Lattice Radiant」や「Lattice Diamond」を提供する。ニューラルネットワークコンパイラを用いることで、標準的なフレームワークを用いて構築したネットワークを、RTLの知識がなくてもFPGAに組み込むことができるという。

レファレンスデザインとしては、MDP向けに顔検出やキーフレーズ検出の機能、VIP向けにオブジェクトカウント、顔追跡、速度標識検出を行う機能などを用意した。これら以外についても、認定パートナーとのエコシステムにより、スマートホームやスマートシティー、スマートファクトリーなどの用途に向けたカスタムデザインサービスを提供する。

同社は、エッジ製品に向けた半導体デバイス事業にフォーカスしてきた。特に、消費電力が極めて小さく小型で高性能な同社製品は、センサーブリッジとして多くの実績を持つ。今後は、AI技術を搭載したエッジ製品などの用途に期待する。

同社アジアパシフィック地域事業開発担当シニアマネジャーを務める陳英仁(インジェン・チン)氏は、膨大な機器が接続されるIoT(モノのインターネット)の課題として、「データ遅延やプライバシーの問題、そしてバンド幅の制約」を挙げた。これらを解決する方法の1つが、AI技術を搭載したエッジ製品である。これらの製品では、消費電力や部材コストを抑えつつ、既存インタフェースへの対応も必要となる。

「MDPに搭載したiCE40 UltraPlus FPGAは、消費電力が最小1mWでパッケージサイズは5.5mm2、価格は約1米ドルからである。VIPのECP5 FPGAでも消費電力は1W以下と少ない」(陳氏)と、同社のFPGAを利用するメリットを強調した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

エッジコンピューティング、低電力でAI実現

エッジコンピューティング、低電力でAI実現

AI(人工知能)技術をベースとしたエッジコンピューティングを次の成長ドライバーと位置付けるLattice Semiconductor。フォーカスする分野は消費電力が1W以下で、処理性能は1テラOPS(Operations Per Second)までのアプリケーションだ。 超小型FPGAをエッジに、独自路線を進むLattice

超小型FPGAをエッジに、独自路線を進むLattice

小型で低消費電力のFPGAを手掛けるLattice Semiconductorは、クラウド市場に注力する他のFPGAベンダーとは明確に路線を分け、エッジ向けに力を入れる。 USBの代わりの無線コネクターなど主要製品を展示

USBの代わりの無線コネクターなど主要製品を展示

Lattice Semiconductorは、3年ぶりの出展となった「CEATEC JAPAN 2017」で、超小型のFPGAや、USBコネクターの代わりに使える無線コネクター技術など、同社の主要製品を展示した。 ラティス、28nm FD-SOIのFPGA開発を決断

ラティス、28nm FD-SOIのFPGA開発を決断

Lattice Semiconductor(ラティスセミコンダクター)は、IoT(モノのインターネット)エッジ市場に向けた製品展開や事業の方向性を示す中で、28nm完全空乏型SOI(FD-SOI)技術を用いたFPGAのサンプル出荷を2018年中に行う計画であることを明らかにした。 エッジAIで実現する未来、ソシオネクストが提案

エッジAIで実現する未来、ソシオネクストが提案

ソシオネクストは、「第7回 IoT/M2M展【春】」で、エッジコンピューティングによるAI(人工知能)推論システムや監視カメラソリューションを紹介した。 NEDO、AIエッジ・次世代コンピューティング事業を開始

NEDO、AIエッジ・次世代コンピューティング事業を開始

新エネルギー・産業技術総合開発機構(NEDO)は2018年4月20日、「AIチップ・次世代コンピューティングに関する研究開発事業」を新たに開始すると発表した。同事業により、AIエッジチップや次世代コンピューティング分野で国内の研究開発を促進し、日本の情報産業再興を目指すという。