ラティス、FPGAベースのAIスタックを拡張:エッジ製品側でのAI処理を加速

Lattice Semiconductor(ラティスセミコンダクター)は、エッジ製品側にAI(人工知能)機能を導入するための技術スタック「Lattice sensAI」について、その機能拡張を発表した。

CNN小型アクセラレーターIPコアなどを新たに追加

Lattice Semiconductor(ラティスセミコンダクター)は2018年10月11日、エッジ製品側にAI(人工知能)機能を導入するための技術スタック「Lattice sensAI」について、その機能拡張を発表した。「IPコア」や「レファレンスデザイン」「ハードウェア開発キット」などを新たに追加し提供する。

Lattice sensAIは、家電製品や監視カメラ、セキュリティカメラ、マシンビジョンといった、さまざまなIoT(モノのインターネット)製品に、AI技術を搭載しやすくするためのソリューションである。極めて少ない電力消費と部材コストで、AI機能を実装できるのが特長で、2018年5月に発表した。

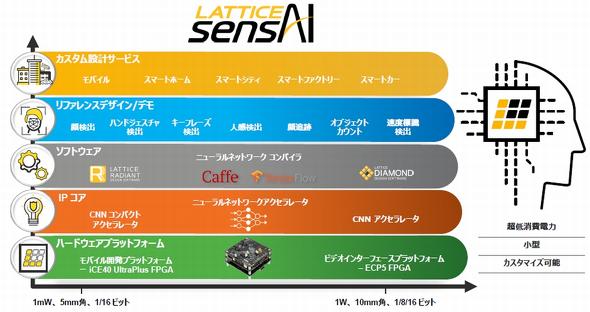

具体的には、同社製FPGAの「iCE40 UltraPlus」および、「ECP5」を用いた「ハードウェアプラットフォーム」、推論処理を行うための「ニューラルネットワークIPコア」、ニューラルネットワークコンパイラなどの「開発ツール」、システム開発を容易にする「レファレンスデザイン」および、「カスタム設計サービス」と、5つのスタックで構成されている。

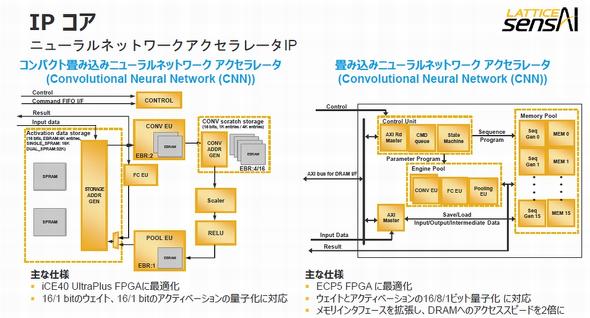

その中で今回、機能拡張を行った1つがIPコアである。これまで「iCE40 UltraPlus」向けには、バイナリーニューラルネットワーク(BNN)アクセラレーターを提供してきた。今回、16ビットと1ビットの量子化に対応したコンパクトな畳み込みニューラルネットワークアクセラレーター(CNN)IPコアを用意した。また、「ECP5」向けに最適化されたCNNアクセラレーターIPコアは、これまで16ビットだったメモリインタフェースを32ビットに拡張した。これによって、DRAMへのアクセス速度は2倍に向上した。

機能拡張の2つ目はソフトウェア開発ツールである。iCE40 UltraPlusに向けたニューラルネットワークコンパイラは、これまでフレームワーク「Caffe」のみ対応していたという。今回はこれに加え「TensorFlow」にも対応できるようにした。

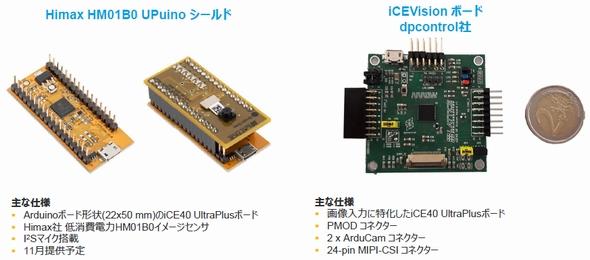

開発プラットフォームとしては、iCE40 UltraPlus用プラットフォーム(MDP)と、ECP5用プラットフォーム(VIP)を用意している。今回、iCE40 UltraPlus用モジュラーハードウェアプラットフォームとして、HiMax製のHM01B0搭載「UPDuinoシールド」や、dpcontrol製「iCeVisionボード」を新たに追加した。顔や人体検出、ハンドジェスチャー検出などを行うためのレファレンスデザインなどを活用すれば、システムの開発や検証を迅速に行うことができる。

カスタムデザインサービスにも力を入れる。SoftnauticsやWiproといった企業に加えて、三栄ハイテックスとポコアポコネットワークスを新たにパートナー企業として追加した。

ラティスセミコンダクターでエリアテクニカルマネジャーを務める粼田寛明氏は、「AIを用いたエッジデバイスは、今後5年間に個数ベースで110%以上のCAGR成長率が予測されている」と話す。こうした中で、エッジAIに求められる要件として、「低消費電力」「少ないコスト追加」「省スペースでの実装」「さまざまなインタフェースへの対応」などを挙げた。

同社は、「Lattice sensAI」を応用した物体検知や車両方向検知、キーフレーズ検出など具多的な事例について、「CEATEC JAPAN 2018」(2018年10月16〜19日、千葉・幕張メッセ)の自社ブースでデモ展示を行う予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

低電力で低コスト、FPGAを活用したAIスタック

低電力で低コスト、FPGAを活用したAIスタック

Lattice Semiconductor(ラティス・セミコンダクター)は、極めて小さい電力消費と部材コストで、エッジ製品へのAI(人工知能)導入を行うことができる技術スタック「Lattice sensAI」を発表した。 エッジコンピューティング、低電力でAI実現

エッジコンピューティング、低電力でAI実現

AI(人工知能)技術をベースとしたエッジコンピューティングを次の成長ドライバーと位置付けるLattice Semiconductor。フォーカスする分野は消費電力が1W以下で、処理性能は1テラOPS(Operations Per Second)までのアプリケーションだ。 超小型FPGAをエッジに、独自路線を進むLattice

超小型FPGAをエッジに、独自路線を進むLattice

小型で低消費電力のFPGAを手掛けるLattice Semiconductorは、クラウド市場に注力する他のFPGAベンダーとは明確に路線を分け、エッジ向けに力を入れる。 ラティス、28nm FD-SOIのFPGA開発を決断

ラティス、28nm FD-SOIのFPGA開発を決断

Lattice Semiconductor(ラティスセミコンダクター)は、IoT(モノのインターネット)エッジ市場に向けた製品展開や事業の方向性を示す中で、28nm完全空乏型SOI(FD-SOI)技術を用いたFPGAのサンプル出荷を2018年中に行う計画であることを明らかにした。