AIプロセッサを開発した東芝メモリの狙い:メモリ以外での勝負も必要に?(1/3 ページ)

東芝メモリは2018年11月6日、ディープラーニング専用のプロセッサを開発したと発表した。今回同社が開発したのは、推論向けの技術。アルゴリズムとハードウェアの協調設計により、従来の方法に比べて認識精度をほとんど劣化させずに演算量を削減し、推論の高速化と低消費電力化を図ることに成功した。

東芝メモリは2018年11月6日、ディープラーニング専用のプロセッサを開発したと発表した。今回同社が開発したのは、推論向けの技術。アルゴリズムとハードウェアの協調設計により、従来の方法に比べて認識精度をほとんど劣化させずに演算量を削減し、推論の高速化と低消費電力化を図ることに成功した。台湾で開催された国際学会「A-SSCC(Asian Solid-State Circuits)」(2018年11月5〜7日)で発表した。

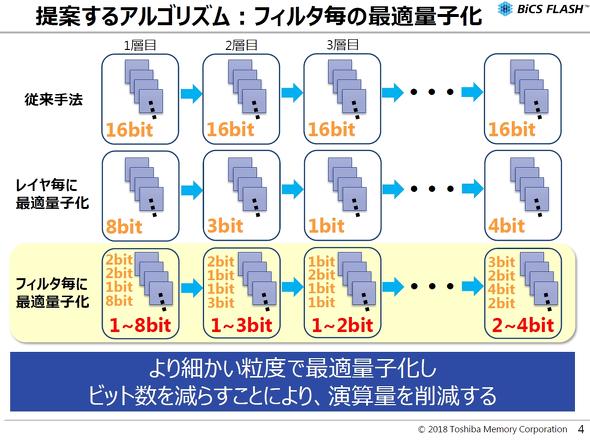

フィルターごとに量子化

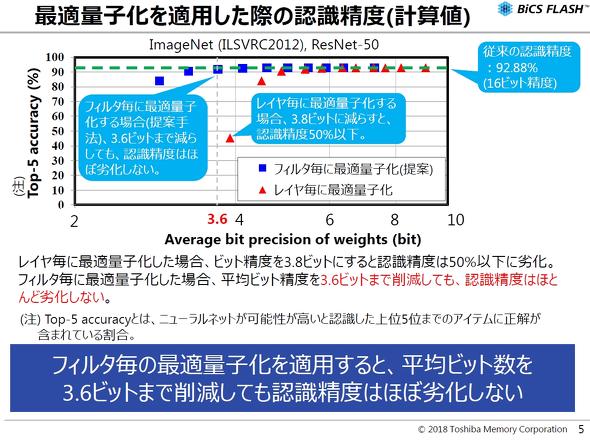

ディープラーニングで認識精度を高めるためには、多くの積和演算が必要になる。だが、積和演算の数が増えるほど、当然、処理時間と消費電力は増大する。この課題に対しては、積和演算で用いる定数(重み)のビット数をレイヤーごとに減らすことで演算量を削減する方法が提案されている。ただ、この方法だと、重みを1ビットや2ビットまで削減すると、認識精度が劣化するというトレードオフが発生する。今回東芝メモリが開発したアルゴリズムは、ニューラルネットワークの各レイヤーに存在する、フィルターごとに最適量子化を行う。従来の提案である、レイヤーごとの最適量子化に比べ、より細かい粒度で量子化することで演算量を削減することができる。

このアルゴリズムを適用した結果、平均ビット精度を3.8ビットにすると認識精度が50%以下に劣化する「レイヤーごとの最適量子化」に比べ、平均ビット精度を3.6ビットまで削減しても、認識精度はほとんど変わらなかった。

Copyright © ITmedia, Inc. All Rights Reserved.