AIプロセッサを開発した東芝メモリの狙い:メモリ以外での勝負も必要に?(2/3 ページ)

東芝メモリは2018年11月6日、ディープラーニング専用のプロセッサを開発したと発表した。今回同社が開発したのは、推論向けの技術。アルゴリズムとハードウェアの協調設計により、従来の方法に比べて認識精度をほとんど劣化させずに演算量を削減し、推論の高速化と低消費電力化を図ることに成功した。

まるでテトリス、「ビットパラレル」

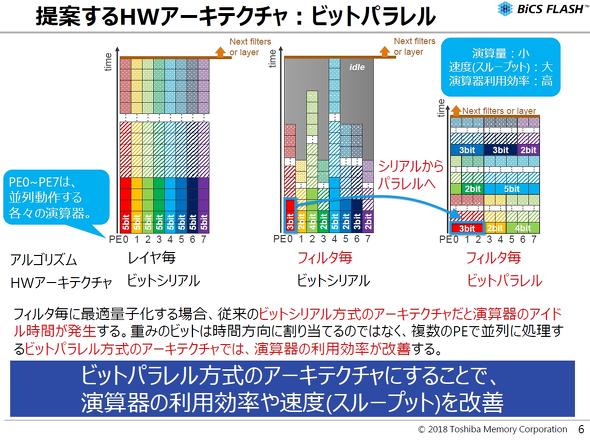

ハードウェアアーキテクチャとしては、「ビットパラレル方式」を提案する。レイヤーごとの最適量子化では、複数の演算器において、1ビットずつ時間軸方向に割り当てる「ビットシリアル方式」で演算している。

東芝メモリが開発したアルゴリズムをこのビットシリアル方式に割り当てると、使用するビット数は減るものの、そのフィルター内の最大ビット数の演算が完了するのを待たなければならないため、演算器の利用効率が落ちてしまう。さらに、リーク電流も流れてしまうので消費電流が発生する。

それに対し、ビットパラレル方式では、1ビットに分解し、それを各演算器に順番に割り当て、並列動作させる。これによって、演算器の利用効率はほぼ100%に高まり、処理速度(スループット)も高まる。

「ビットパラレル方式」のアーキテクチャ。左=従来のビットシリアル方式は、各演算器(PE:Processing Element)において時間軸方向(縦軸方向)に1ビットずつ積み上げていくようなイメージ/中央=フィルターごとの最適量子化を、ビットシリアル方式に適用させると、1個当たりで演算するビット数は減るものの、全体としてみると利用効率がよくない/右=ビットパラレル方式は、1ビットずつに分解し、各PEに順番に割り当てていく。「テトリス」のように、PEが休むひまなく演算するよう、隙間を埋めていくようなイメージだ 出典:東芝メモリ(クリックで拡大)

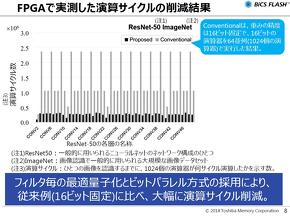

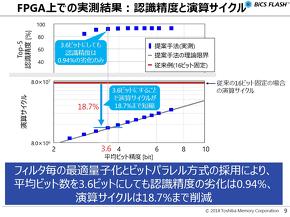

東芝メモリは、開発したアルゴリズムを、ハードウェアアーキテクチャを用いてFPGAに実装。実際に演算した結果、重みの精度を16ビットに固定した従来の演算に比べ、演算サイクル数を大幅に削減できることが分かった。具体的には、認識精度をほぼ同等レベルに維持しつつ、演算サイクルを約18.7%に削減。これにより、スループットは従来の約5.3倍、消費エネルギーは約18.7%に改善した。

開発したアルゴリズムを、ハードウェアアーキテクチャを用いてFPGAに実装した。Xilinxの「Zynq UltraScale+ MPSoC」の評価キット「ZCU102」を用いた。この例では「ウサギ」ということだけでなく、ウサギの種類まで判別しているという 出典:東芝メモリ(クリックで拡大)

なお、今回開発したアルゴリズムは、学習したモデルに対して量子化するので、学習にかかるコストや時間はこれまでと変わらない。

Copyright © ITmedia, Inc. All Rights Reserved.