3D NANDの高密度化を支えるペア薄膜のスケーリング手法:福田昭のストレージ通信(127) 3D NANDのスケーリング(13)

「IMW(International Memory Workshop)」のショートコースから、3D NANDフラッシュメモリ技術に関する講座を紹介するシリーズ。今回からは、3D NANDフラッシュの高密度化と大容量化の手法(スケーリング手法)と、時間的なスケジュール(ロードマップ)をご紹介していく。

スケーリング手法とロードマップを紹介へ

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの前回では、3D NANDフラッシュ製造における重要技術(キープロセス)である、「絶縁膜の埋め込み(Isolation Fill)」技術と、「平坦化(Planarization)」技術を解説した。今回からは、3D NANDフラッシュの高密度化と大容量化の手法(スケーリング手法)と、時間的なスケジュール(ロードマップ)をご紹介していく。

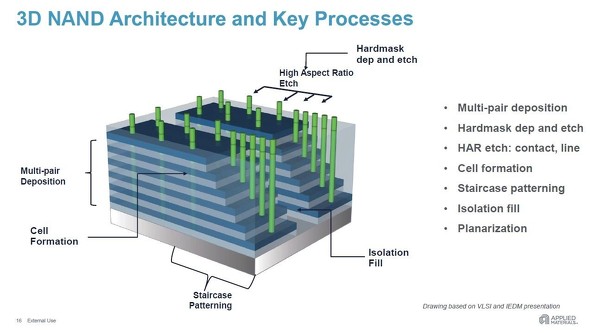

3D NANDフラッシュメモリの立体構造図と、重要な製造技術(「キープロセス」)。「キープロセス」には、「多ペア薄膜(Multi-pair)の成膜(Deposition)」「ハードマスク(Hardmask)の成膜とエッチング」「高アスペクト比(HAR:High Aspect Ratio)のエッチング」「メモリセルの形成(Formation)」「ステアケース(Staircase)のパターン形成」「絶縁膜の埋め込み(Isolation Fill)」「平坦化(Planarization)」などがある 出典:Applied Materials(クリックで拡大)

ペア薄膜の積層数を増やすのが高密度化の基本手法

前回までに説明したキープロセスの中で、スケーリング手法として重要な指標が「ペア薄膜」の積層数と寸法である。復習の意味で再掲すると「ペア薄膜」とは、絶縁層と制御ゲート層(ワード線層)を交互に積層した薄膜のことである。3D NANDフラッシュの製造では、このペア薄膜を数多く積み上げることで、セルストリングを垂直方向に形成する。具体的には1個の制御ゲート層が、1個のセルトランジスタに対応する。

そして高密度化手法の中で最も重要であり、かつ基本的な手法が、「ペア薄膜の積層数を増やすことによって、セルトランジスタの数を垂直方向に増やすこと」である。3D NANDフラッシュメモリの高密度化をこれまでけん引し、なおかつ今後もけん引するのは、「ペア薄膜の積層数の増加」であることは間違いない。

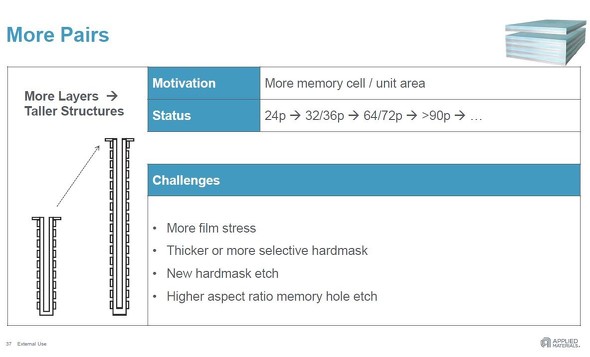

制御ゲート薄膜1層と絶縁薄膜1層のペアを1ペア(ワンペア)とすると、商業化が始まったのは24ペアからである。そしてこれまでペア数は、32/36ペア、48ペア、64/72ペア、90ペア(96ペア)と急激に増えてきた。今後は100ペアを超えるペア数によって、記憶密度の向上を図る。

もちろん課題はある。まず、メモリスルーホール(メモリホール)のエッチングにおけるアスペクト比が増加することにより、エッチングが難しくなる。そしてペア数の増加は、ペア薄膜に加わる応力の増大をもたらす。またエッチング用ハードマスクが厚くなるとともに、より高い選択性が求められる。これらの課題を解決しつつ、ペア数を増やしていくことになる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

絶縁膜の埋め込みと平坦化が、複雑な形状の加工を支える

絶縁膜の埋め込みと平坦化が、複雑な形状の加工を支える

3D NANDフラッシュ製造における重要技術(キープロセス)の一つである「絶縁膜の埋め込み(Isolation Fill)」技術と、「平坦(へいたん)化(Planarization)」技術を紹介する。 Intelの創業4年目(前編)、半導体メモリのトップベンダーに成長

Intelの創業4年目(前編)、半導体メモリのトップベンダーに成長

Intelの創業4年目(1971年)は、「飛躍の年」となった。不揮発性メモリとマイクロプロセッサという、2つの画期的な製品を開発したのだ。前編では、この2製品と、本社社屋の移転について紹介する。 化合物レーザーをシリコンにモノリシック集積する試み(前編)

化合物レーザーをシリコンにモノリシック集積する試み(前編)

本シリーズも、いよいよ最終章となる。最後は、シリコン基板に、化合物半導体レーザーをモノリシックに集積する試みを、前後編にわたって解説する。 2018年の半導体売上高、過去最高となる見込み

2018年の半導体売上高、過去最高となる見込み

SEMIによると、2018年における半導体売上高は4700億米ドルに達し、2017年に続き過去最高を更新する見込みだという。