折り曲げ可能なスマホから3D DRAMまで、SEMIイベント:ISS 2019(2/2 ページ)

エンジニアたちは現在、折りたたみ式スマートフォンや折り曲げ可能なディスプレイ、次世代DRAMなどの実現に向けて取り組む上で、大きな課題に直面している。しかしそこには、新しいクラスのヘルスケアデバイスや3Dチップスタックを提供することが可能な、数々のチャンスが広がっている。

DRAMの3次元化

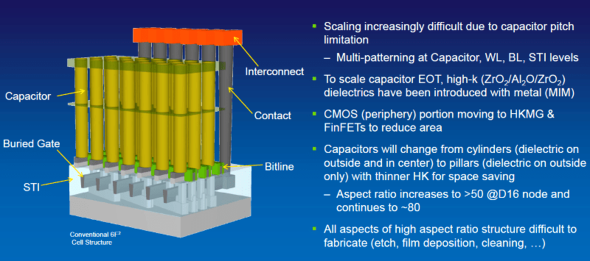

東京エレクトロン(TEL)のコーポレートイノベーション部門担当副部長を務めるAki Sekiguchi氏は、「既存のDRAM技術は、微細化の限界に達しつつある」と指摘する。

TELは微細化に不可欠な技術として、表面張力がゼロになる超臨界乾燥法を採用することを挙げる。表面張力が存在すると、パターンが倒れてしまうからだ。

Micron Technologyのグローバルフロントエンドオペレーション担当マネジャーを務めるBuddy Nicoson氏は、個別インタビューの中で、「当社は今後数年間で、変曲点を迎えることになるだろう。DRAM向けの新しいアーキテクチャの中で、さまざまな取り組みを進めているところだ」と述べる。

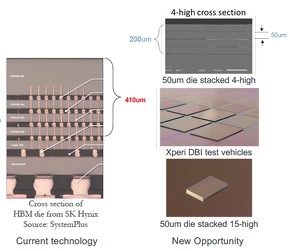

DRAMが3D(3次元)化を実現する手法の一つは、チップレベルでのスタックだ。HBM(High Bandwidth Memory)技術はこれまで、1つのスタック当たり4つの半導体チップまでに制限されていたが、新しいJEDEC規格では、最大12個の半導体チップを積層することが可能になる見込みだ。

Xperiのインターコネクトの専門家は、同社の研究所において、15個のダイを積層したDRAMスタックを実現したとして、その手法について説明している。「Wafer-to-Wafer(WTW)」技術を適用することにより、強力な接続を実現したという。

Xperiで3D/研究開発部門担当バイスプレジデントを務めるPaul Enquist氏は、「ここ10年の間、CMOSイメージャ向けチップスタックでは、いわゆるハイブリッド結合が採用されてきた。この手法は、HBM DRAMの他にも、3D NANDスタックでの使用や、より精度の高いLiDARに向けたグローバルシャッター機能での使用も検討されている」と述べる。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

量子ドットは次世代ディスプレイ向き、材料開発も進む

量子ドットは次世代ディスプレイ向き、材料開発も進む

NSマテリアルズは、「第28回 液晶・有機EL・センサ技術展(ファインテック ジャパン)」(2018年12月5〜7日、幕張メッセ)で、「量子ドットデバイスの現状と展望」と題した技術セミナーに登壇した。 折り曲げられるArduinoも誕生、“FHE”の可能性

折り曲げられるArduinoも誕生、“FHE”の可能性

SEMIジャパンは2018年4月9日、「2018FLEX Japan / MEMS & SENSORS FORUM」の事前記者会見を都内で開催し、同イベントで中核となるフレキシブルハイブリッドエレクトロニクス(FHE)について技術解説と市場動向の紹介を行った。 折り曲げられるスマホ、2019年にも登場か

折り曲げられるスマホ、2019年にも登場か

成熟しつつあるモバイル市場を、再活性化するための取り組みの一環として、2019年には、タブレットとしても使用可能な折りたたみ式スマートフォンが登場するとみられている。 DRAMとNANDフラッシュのベンダー別シェア

DRAMとNANDフラッシュのベンダー別シェア

2018年に開催された「フラッシュメモリサミット」では、さまざまな講演が行われた。今回から始まるシリーズでは、半導体メモリ市場を分析した講演「Flash Market Update 2018」の内容を紹介する。 「不揮発性DRAM」へのアプローチ(前編)

「不揮発性DRAM」へのアプローチ(前編)

今回から、「不揮発性DRAM」の実現を目指す研究開発について解説する。二酸化ジルコニウムは、その結晶構造から、工夫次第で強誘電体のような不揮発性を付加できる可能性がある。 CMOSイメージセンサーにDRAMを積層

CMOSイメージセンサーにDRAMを積層

ソニーは、DRAMを積層した3層構造の積層型CMOSイメージセンサーを開発した。高速読み出しを実現したことで、スマートフォンでもスーパースローモーション動画の撮影などが可能となる。