次世代メモリの考案から製品化まで:「ステルス」モードの研究開発:福田昭のストレージ通信(143) 半導体メモリの技術動向を総ざらい(6)(2/2 ページ)

次世代メモリの発案から製品化までは10年近くかかる。今回は、その道のりの後半部分として、設計ルールの選択やサンプル試作、量産までのステップを説明する。

試作完了から製品化、そして量産までのステップ

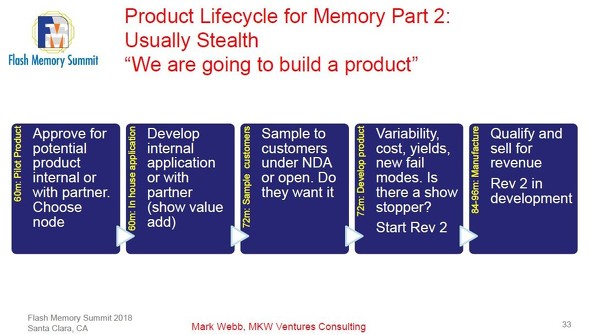

ここからは後半部分の手順を説明していこう。メモリセルアレイの試作結果が良好な場合、製品化に向けて開発を進める。ベンチャー企業の場合は、提携先企業(パートナー企業)と相談して製品化を決定することが少なくない。ここで重要なのは、製品化のプラットフォームとなる半導体製造技術(設計ルール)を選択することである。

微細な製造技術はウエハー当たりのコストが高くなるものの、シリコンダイ面積が小さくなるのでウエハー当たりの収量(ダイの枚数)が多い。緩やかな製造技術はウエハー当たりのコストは低いけれども、シリコンダイ面積が大きくなるのでウエハー当たりの収量(ダイの枚数)は少ない。ここには製品の付加価値と、目指す応用の市場規模が絡んでくる。製造技術の選択は容易ではない。製造技術の選択と用途開拓までで、研究開発がスタートしてからの期間は5年(60カ月)に達するだろう。

次に来るのは、サンプルを試作して顧客の有力な候補に評価してもらうことである。顧客の候補による評価と要望のフィードバックは欠かせない。それから製造のばらつきやコスト、歩留まり、不良モードなどを点検しつつ、量産の準備に入る。製品化を阻害するような大きな問題(show stopper)が存在していないことも、確認する必要がある。また並行して、第2世代品の開発に着手することも重要だ。ここまでで、スタートしてから6年(72カ月)が経過していると思われる。

そして顧客候補による認証を経て、製品の販売と量産が始まる。並行して第2世代品の開発を本格化させる。この段階で、開発が始まってから7年(84カ月)〜8年(96カ月)の期間が過ぎているだろう。

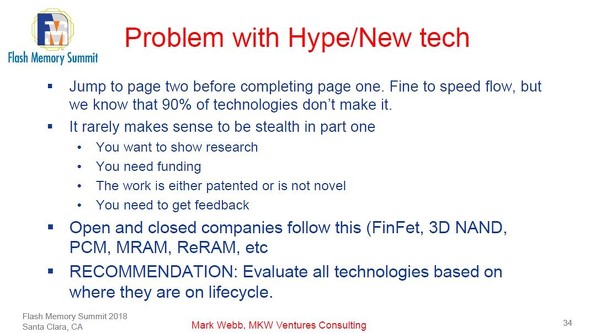

このように、研究開発の道のりは短くない。研究開発の期間を短縮する方法として起こるのが、前半をスキップすることだ。地道な作業である前半をスキップし、最初から後半に突入して製品化を進める。しかしこのやり方だと、多くの場合は上手くいかない。焦りは禁物だといえる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

次世代メモリの「理想と現実」

次世代メモリの「理想と現実」

今回は次世代メモリの理想と現実の違いを述べるとともに、コンピュータのメモリ階層における次世代メモリの立ち位置をご説明する。 DRAMのスケーリング論

DRAMのスケーリング論

今回はDRAMのスケーリングと、次世代メモリへのニーズが高まっている背景を取り上げる。 Samsung、19年Q1の業績は大幅悪化 メモリ不況で

Samsung、19年Q1の業績は大幅悪化 メモリ不況で

Samsung Electronics(以下、Samsung)は、DRAMおよびNAND型フラッシュメモリチップの価格が継続的に下落する中、2019年第1四半期の売上高、利益とも大幅に減少する見込みだ。 清華紫光集団がSMICのCEOを引き抜きか、DRAM強化で

清華紫光集団がSMICのCEOを引き抜きか、DRAM強化で

中国のほぼ全ての半導体資産を管理する国有持ち株会社Tsinghua Unigroup(清華紫光集団、以下Tsinghua)は、中国国内のDRAM業界を再構築すべく、SMIC(Semiconductor Manufacturing International Corporation)の共同CEO(最高経営責任者)であるHaijun Zhao氏を引き抜く考えのようだ。 メモリを取り巻く状況、19年後半には改善へ Micron

メモリを取り巻く状況、19年後半には改善へ Micron

2018年における半導体メーカー売上高ランキングで第4位、米国企業としてはIntelに次ぐ2位を獲得した、メモリメーカーのMicron Technology(以下、Micron)。同社で、Executive Vice President兼CBO(Chief Business Officer)を務めるSumit Sadana氏に、今後の投資予定や製品戦略などを聞いた。 超低消費電力のシリアルフラッシュ、標準品比で70%減

超低消費電力のシリアルフラッシュ、標準品比で70%減

Adesto Technologies(以下、Adesto)は、組み込み技術の国際展示会「embedded world 2019」(2019年2月26〜28日、ドイツ・ニュルンベルク)で、2月25日(米国時間)に発表したばかりの不揮発性メモリ「Fusion HD(Higher Density)」のデモを展示した。