組み込みAIを加速する、ルネサスの新Processing-in-Memory:低電力で高速な推論を実現する(2/4 ページ)

ルネサス エレクトロニクスは、メモリ回路内でメモリデータの読み出し中に積和演算を行う既存のProcessing-in-Memory(PIM)を改良した、新たなPIM技術を開発したと発表した。同技術をベースに開発したAIアクセラレーターをテストチップに実装して推論処理を行ったところ、8.8TOPS/Wの電力効率を実証したという。

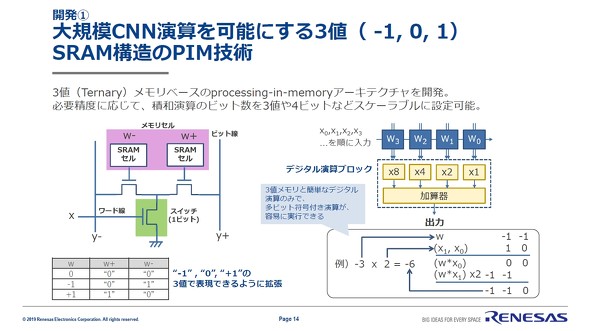

3値のSRAM構造を新たに開発

まず、3値(−1、0、1)のSRAM構造を新たに開発し、これをベースにPIMを構成した。メモリセルの基本構造としては、2本のビット線(ビット線および、ビット線バーとする)の間に2つのSRAMセルと1個のスイッチとなっている。

3値だと、「ビット線に電流を流す」「ビット線バーに電流を流す」「どちらにも流さない」という状態を実現できる。1つのメモリセルで3値の情報を持てるので、重みデータの情報を増やすことができる。つまり、ニューラルネットワークの認識精度が高くなる。また、「どちらにも流さない」という状態を作れるので電流量が減り、低電力化を実現できる。さらに、3値のセルだと、重みデータを任意のビット数に拡張することが容易になるという。

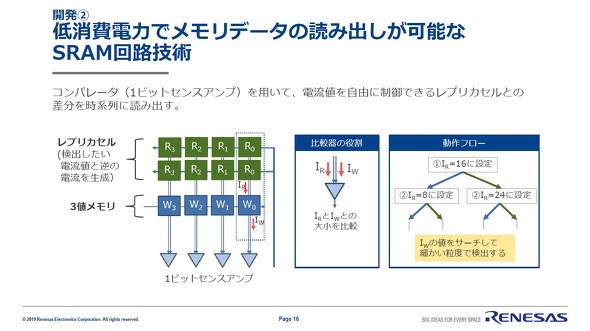

コンパレーターとレプリカセルでA-Dコンバーターを不要に

2つ目として、低消費電力で高精度にメモリデータを読み出す回路を開発した。一般的に、高精度なビット線電流の検出にはA-Dコンバーターを用いることが有効だが、この方法だと消費電力とチップ面積が増大してしまう。そこでルネサスは、コンパレーター(1ビットセンスアンプ)と、電流値を自由に制御できるレプリカセルを用いることで、A-Dコンバーターを使わずに高精度にメモリデータを読み出せる回路を開発したという。

上の図で、W0から流れている電流(IW)をコンパレーターで検知する場合、レプリカセル側から、逆のビット線に数段階の電流を複数のパターンで流し、どこでコンパレーターが反転するかをサーチすることで、IWを検出できる。また、図の右側の「動作フロー」に示すように、二分岐探索を行うことで、高速にサーチできるようにしたという。

この他、活性化しているノード(ニューロン)はごく一部であることを利用して、非活性化ノードでは読み出し回路自体の動作を停止し、さらなる低電力化も図れるとする。

Copyright © ITmedia, Inc. All Rights Reserved.