組み込みAIを加速する、ルネサスの新Processing-in-Memory:低電力で高速な推論を実現する(3/4 ページ)

ルネサス エレクトロニクスは、メモリ回路内でメモリデータの読み出し中に積和演算を行う既存のProcessing-in-Memory(PIM)を改良した、新たなPIM技術を開発したと発表した。同技術をベースに開発したAIアクセラレーターをテストチップに実装して推論処理を行ったところ、8.8TOPS/Wの電力効率を実証したという。

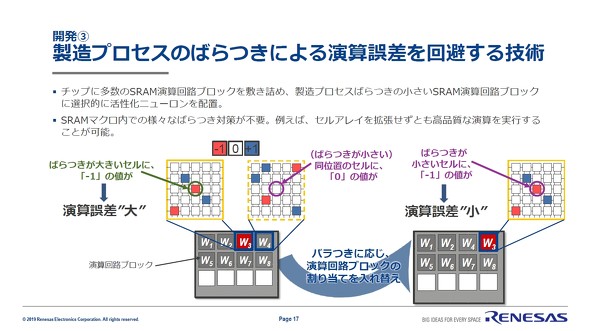

演算回路ブロックを入れ替えて製造ばらつきを低減

3つ目が、製造プロセスのばらつきによる演算誤差を回避する技術の開発だ。製造プロセスがばらつくと、ビット線電流の値に誤差が生じ、それがメモリデータ読み出しの誤差につながってしまう。例えば、ばらつきが大きいメモリセル(異常に大きな電流を流してしまうメモリセル)に「−1」や「+1」といった重みデータが格納されてしまうと、積和演算の結果が大きく違ってしまう可能性がある。一方で、もしそのセルに格納されている重みデータが「0」ならば、掛け算の結果は常にゼロになるので電流は流れず、積和演算の結果に影響がない。

新しいPIMでは、この原理を利用したという。チップに多数のSRAM演算回路ブロックを敷き詰め、ばらつきの大きいセルに「−1」や「+1」の重みデータが格納されたブロックがあった場合、すぐ隣のブロックと重み情報を入れ替えるという仕組みだ。

前述したように、活性化しているニューロンは基本的に極めて少ない。そのため、ほとんどの3値セルには「0」が格納されている。つまり、隣のブロックの同じ番地には『0』が入っている確率が非常に高い。ブロックを入れ替えれば、ばらつきが大きいセルに『0』が入る可能性が高く、掛け算の結果をゼロにできるのだ。

ただし、野瀬氏によると、メモリセルのばらつきを検出する方法は「検討中」だという。

図の「W1」「W2」などが演算回路ブロック。この中に、3値メモリセルが入っている。ばらつきに応じて、演算回路ブロックを隣のブロックと、そっくりそのまま入れ替えることで、演算誤差を回避できるとする 出典:ルネサス(クリックで拡大)

「演算回路ブロックを入れ替えるだけでいいので、冗長セルなどを入れずに演算誤差を大幅に低減できる」(野瀬氏)

Copyright © ITmedia, Inc. All Rights Reserved.