Intelが3つの次世代パッケージング技術を明らかに:SEMICON West 2019(1/2 ページ)

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。この3つの中で最も興味深い技術が、Intelが現在、米国エネルギー省向けに製造を進めているエクサスケールスーパーコンピュータ(スパコン)で採用されるとみられる。

現在、従来のような半導体の微細化が行き詰まり、コストが増大の一途をたどっているという状況の中、Intelはこれらの3つの技術によって、自社のプロセッサの優位性を確立していきたい考えだ。

まずIntelは、2018年にDARPAプログラムの一環として発表したチップレット向けの物理インタフェース「AIB(Advanced Interface Bus)」の次世代版となる「MDIO(Multi-Die IO)」を発表した。同社は2020年中に、MDIOをチップスタックで使用する予定だが、スペックに関する発表をいつ行うのかは未定だという。

Intelは、「MDIOは、TSMCが2019年6月に行われた半導体のデバイス技術/回路技術の国際会議『VLSIシンポジウム』において発表したチップレットインタフェース『LIPINCON(Low-voltage-In-Package-INterCONnect)』に対して、競争力を持っている」と主張する。

エクサスケールスパコンに採用予定の「Co-EMIB」

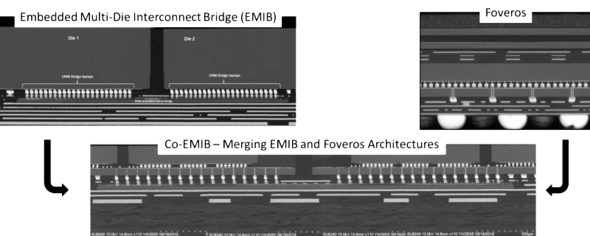

新しい3つの技術の中でも最も興味深いのが、Intelの最新型の2D/3D積層技術を組み合わせた「Co-EMIB」だ。Intelは、米スパコン企業のCray(HPEが買収を発表)と共同でエクサスケールスパコン「Aurora」の開発を進めているが、このAuroraに搭載されるCPUとGPUコアを接続するための手段として、初めて採用されるとみられる。

Co-EMIBは、Intelが2018年12月に発表した3D積層チップ技術「Foveros」と、Intel独自の高密度パッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を組み合わせたものになっている。

Intelによれば、EMIBを採用したFPGA「Stratix X」やCPU(「Kaby Lake G」)を搭載したデバイスの出荷数量は既に約100万台に上るという。2020年には、ノートPC向けの統合型プロセッサ「Lakefield」を出荷する予定で、これは同社のFoveros技術を採用した初めてのチップとなる。

Intelは現在、Foverosを使って積層するに当たり、輸送の遅れで苦しんでいるという。製造プロセスが、米国オレゴン州のフロントエンドの製造ラインと、アリゾナ州のバックエンドの製造ラインとに分かれているからだ。1カ所に集約できれば、ターンアラウンドタイムは約2週間になるはずだという。

Copyright © ITmedia, Inc. All Rights Reserved.