半導体製造プロセスは継続的な進化を:実用化されたEUV(1/2 ページ)

EUV(極端紫外線)リソグラフィの開発プロセスは、長期にわたって難しい道のりを進んできた。EUV開発については、EUVの新しいパターニング性能を採用するかしないかによって、半導体チップ製造プロセスが将来的にどのような技術になるのかを、一歩引いた所から検討する必要があるのではないだろうか。

EUV(極端紫外線)リソグラフィの開発プロセスは、長期にわたって難しい道のりを進んできた。

数十年に及ぶ献身的な取り組みが行われた結果、現在では、製造に適用できるような技術となった。しかし、「技術が導入可能な状態にある」ということが、必ずしも「導入すべき技術である」ことを意味するわけではない。EUV開発については、EUVの新しいパターニング性能を採用するかしないかによって、半導体チップの製造プロセスが将来的にどのような技術になるのかを、(実践的な製造実績が拡大しているという状況を踏まえて)一歩引いた所から検討する必要があるのではないだろうか。

7nmプロセスによる製造は、マルチパターニング技術の採用により、EUVなしで確実に実行することができるが、このような手法では現在、製造プロセス全体に対して、ターンアラウンドタイムに関するペナルティを課すことになる。これは、半導体メーカーが自社の顧客企業に対応するための能力として非常に重要な、市場投入までの時間などにも、影響が及ぶ可能性があるということだ。

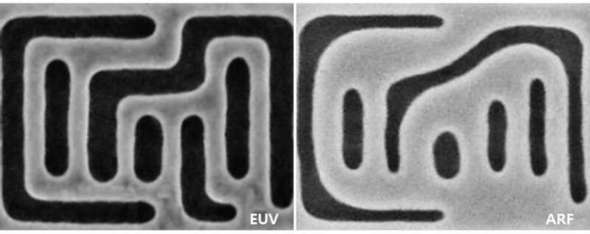

また、波長が193nmのマルチパターニング技術から、13.5nmと短いEUVに移行することで、EPE(Edge Placement Error)の低減やパターン忠実度の向上などを実現できるようになる。いずれの効果も、現在だけでなく将来的に、デバイスの性能や歩留まりなどに大きなメリットをもたらすだろう。

さらに広い観点から見ると、EUVによって簡素化が実現されることにより、製品開発者たちは、193nm液浸リソグラフィからなんとか利用価値を絞り出したトリプル/クアッドパターニング技術を扱わなければならないという、一種の強迫観念のようなものから解放され、負担を減らせるようにもなるだろう。

EUVが、半導体製造分野が現在直面している基本的な技術課題を解決する上で、適用可能な唯一の実践的手法であるのは明らかだ。独自の課題への取り組みが増えている顧客企業に対して、負担を軽減できるようサポートすることが可能だ(例えば、かなりの長期にわたるデバイス開発期間や、数億米ドル規模に達する開発コストなど)。

Copyright © ITmedia, Inc. All Rights Reserved.