米ADIで働く日本人技術者に聞く、オペアンプの地道な進化:デジタルとアナログの“最先端”は違う(1/2 ページ)

AI(人工知能)や5G(第5世代移動通信)といったトレンドに後押しされ、技術の進化や競争の激化が著しいデジタルICの分野に比べ、アナログICは比較的ゆっくりと、だが着実に成長を続けている分野だ。ここ数年で、アナログ技術にはどのような進化があったのか。Analog Devices(ADI) でシニアスタッフデザインエンジニアを務める楠田義憲氏に、オペアンプの技術動向や、旧Linear Technologyとの合併後の開発体制などを聞いた。

AI(人工知能)や5G(第5世代移動通信)といったトレンドに後押しされ、技術の進化や競争の激化といった話題が多いデジタルICの分野に比べ、アナログICは比較的ゆっくりと、だが着実に成長を続けている分野だ。ここ数年で、アナログ技術にはどのような進化があったのか。アナログ大手のAnalog Devices(ADI) リニアプロダクツ&ソリューションズグループでシニアスタッフデザインエンジニアを務める楠田義憲氏に、オペアンプの技術動向や、旧Linear Technologyとの合併後の開発体制などを聞いた。

バイポーラからCMOSへ

EE Times Japan(以下、EETJ) まずはオペアンプ技術の動向と進化について教えてください。

楠田義憲氏 プロセスでいえば、まず20〜30年前にロジックICが、次にA-Dコンバーターが、バイポーラからCMOSへと移り変わった。そして、ここ5年くらいでCMOS化が進み始めたのが、センサーフロントエンド(センサーからアナログ信号を受け、増幅して処理を行い、A-Dコンバーターに信号を渡す部分)だ。

その背景として、プロセス技術の進化と回路技術の進化が挙げられる。プロセス技術では、比較的安価なCMOSプロセスをベースとした、高耐圧、高精度のプロセスを使えるようになった。ここでいう高耐圧は、電源電圧が30Vなどだ。それ以前のCMOSプロセスの電源電圧は5Vだった。そこから微細化が進み、3.6V、1.8Vと低くなり、近年は1Vを切るような微細プロセスも出てきている。

だが、センサー信号処理で求められているアナログ技術は、上記の流れとは逆行している。10V以上の電源電圧で動作するセンサーが依然として多いからだ。しかも、物理的な特性によるものなので、低くはならない。そのため、センサーとのインタフェースとして機能するアナログオペアンプICは、高耐圧のバイポーラプロセスが必要だった。

それが近年、30Vを超える高耐圧CMOSプロセスが使えるようになってきた。

CMOSプロセスでは、微細化や、プロセッサのトランジスタ密度などがどうしても注目されるので、“微細な方が最先端だ”という着眼点になりがちだが、われわれが携わるセンサーインタフェースとしてのアナログ回路では、微細化ではなく、高耐圧、高精度、安価、壊れにくいといった点が“最先端”になる。

EETJ CMOSプロセスへの置き換えに、何か課題はありますか。

楠田氏 バイポーラのデバイスと比べた場合、CMOSデバイスは、コストは低いが、オペアンプで重要な性能の一つであるオフセットエラーや低周波ノイズのエラーが10倍以上悪くなってしまうという点だ。

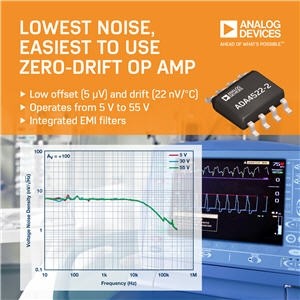

それを解決するための回路技術が、ゼロドリフト技術と呼ばれるものだ。スイッチングのクロックを使って、オペアンプのオフセットエラーを定期的に検出し、補正する。このゼロドリフト技術を採用したオペアンプ(ゼロドリフト・アンプ)は、今のところ、ADIの他には限られた数の競合しか市場に投入していない。

ゼロドリフト技術を使うと、バイポーラを使った従来のプロセスよりも約10倍優れているという結果が出ている。ノイズに関しては、設計によって、バイポーラの方がよい時もあれば、CMOSの方がよい時もある。

CMOSプロセスに置き換わってきたとはいえ、アプリケーションによって従来のバイポーラが必要な時もあるので、両方のプロセスが必要だと考えている。

EETJ では、CMOSがバイポーラを完全に置き換わるというわけではないのですね。

楠田氏 一般的にはそうだが、私はCMOSプロセスを用いる設計者なので、個人的な究極の目標としては、私の設計したデバイスで完全にバイポーラからの置き換えたいという思いはある(笑)。反対に、バイポーラプロセスを用いる当社の設計者は、CMOSデバイスに駆逐されないようなデバイスを設計すればいいのでは。そうやって切磋琢磨して、どちらの性能も上げていけばよいと思う。

EETJ コスト面ではどうなのでしょう。

楠田氏 一般的にはCMOSデバイスの方が安価だといわれている。ざっくり言うと、価格差で2倍ほどではないか。

バイポーラもCMOSも、どちらも使えるという設計者であれば、価格的にCMOSデバイスの方が有利になってくるという可能性はある。ただ、現状、数十年アナログ回路を設計しているユーザーは、バイポーラを使っている場合が圧倒的に多い。2019年7月に当社が開催したセミナーに登壇した際には、「ゼロドリフトアンプはクセが強く、なかなか使い慣れない」という声も聞いた。

EETJ クセが強いというのは、具体的にはどういうことでしょうか。

楠田氏 ゼロドリフトアンプではクロックを使って補正しているが、そのクロックから出てくるスイッチングノイズが問題になる。

ただ、ゼロドリフトアンプを使う際の注意点を守っていただければ、例えば100あるアプリケーションのうち90くらいまでは、ノイズが問題ないレベルで設計できると考えている。残りの10については、われわれICの設計者側とアプリケーション開発者側で議論を重ね、改善していく余地は大いにある。

Copyright © ITmedia, Inc. All Rights Reserved.