微細配線が可能なFO-WLPの組み立て技術:福田昭のデバイス通信(218) 2019年度版実装技術ロードマップ(29)(1/2 ページ)

前回に続き、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。今回は、微細配線を形成可能なFO-WLPを取り上げる。

FO-WLPの再配線層がもたらす多ピン化の限界

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第29回である。

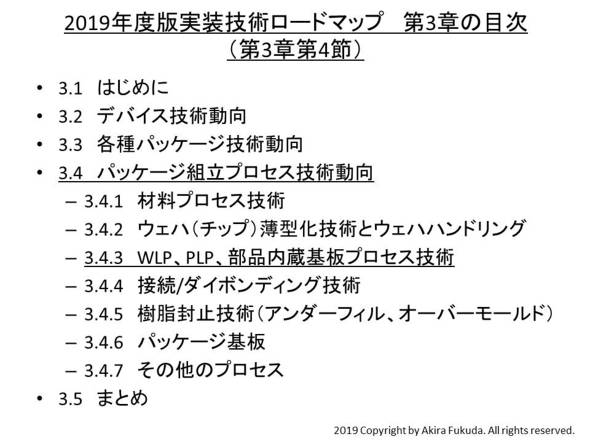

本シリーズの第23回から、第3章「電子デバイスパッケージ」の概要を紹介している。「電子デバイスパッケージ」は第1節から第5節までの5つの節によって構成される。「3.1 はじめに」「3.2 デバイス技術動向」「3.3 各種パッケージ技術動向」「3.4 パッケージ組立プロセス技術動向」「3.5 まとめ」である。前々回から、第3章第4節「3.4 パッケージ組立プロセス技術動向」の概要をご紹介している。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第23回から第3章「電子デバイスパッケージ」(プログラムの7番)の概要を解説している。出典:JEITA(クリックで拡大)

前回は、多ピン対応と小型・薄型・低コストを両立させた「FO-WLP(Fan Out-Wafer Level Package)」の組み立て工程を説明した。今回は、微細配線を形成可能なFO-WLPの組み立て工程をご紹介する。

前回で説明した標準的なFO-WLPにおける再配線層の線幅/間隔は通常、20μm/20μm以上である。最小でも10μm/10μmだといわれる。これはモールド樹脂の硬化収縮、シリコンと樹脂の熱膨張係数の違いによる疑似ウエハーおよびパネルの反り、シリコンと樹脂の熱膨張係数の違いによるシリコンダイの位置ずれ、などの問題によるものだ。線幅/間隔の微細化限界は、多ピン化の実用的な限界を意味する。ピン数があまりに増えると、パッケージが巨大化してしまうからだ。

そこで再配線層の線幅/間隔を10μm未満に微細化した構造のFO-WLPが開発されている。この構造だと、1000ピンを超える端子を実用的な大きさで収容可能になる。

Copyright © ITmedia, Inc. All Rights Reserved.