Xilinxの「ACAP」第3弾、FPGA22個分のロジック集積度:多数のネットワークIPを統合(1/2 ページ)

Xilinxは2020年3月10日(米国時間)、7nmプロセスを適用するデバイス「ACAP(エーキャップ)」の新シリーズとして、データセンターや有線通信向けとなる「Versal Premium(プレミアム)」を発表した。2019年6月に出荷した「Versal AI Core」「Versal Prime(プライム)」の両シリーズに続く第3弾製品となる。

新カテゴリのデバイス「ACAP」の第3弾

Xilinxは2020年3月10日(米国時間)、7nmプロセスを適用するデバイス「ACAP(エーキャップ)」の新シリーズとして、データセンターや有線通信向けとなる「Versal Premium(プレミアム)」を発表した。2019年6月に出荷した「Versal AI Core」「Versal Prime(プライム)」の両シリーズに続く第3弾製品となる。

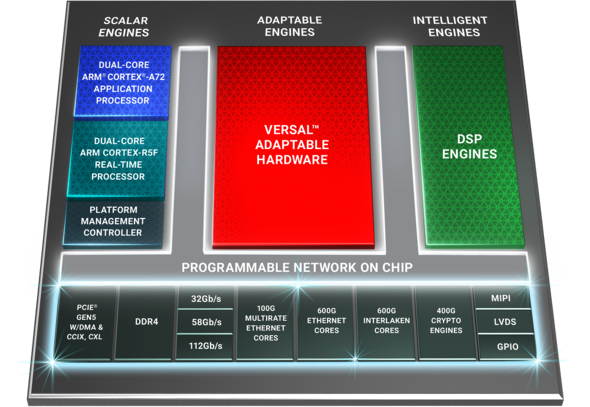

ACAPは、Armプロセッサで構成される「スカラーエンジン」、7nmプロセスを適用したプログラマブルロジックとメモリセルから成る「適応型エンジン」、DSPエンジン/AI(人工知能)エンジンから成る「インテリジェントエンジン」の3つが搭載されたデバイスである。

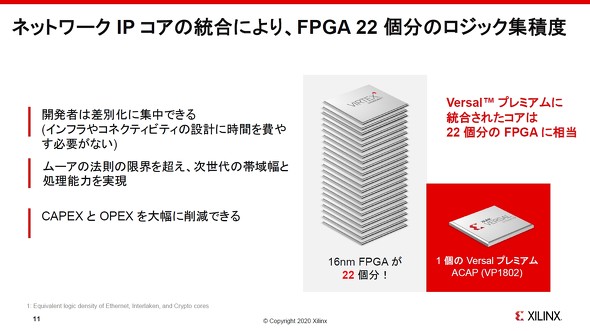

今回発表したVersal Premiumは、Versal Primeをベースに、ネットワークIP(Intellectual Property)コアを統合したものとなる。具体的には、400Gビット/秒(bps)の高速暗号化エンジン、600GbpsのInterlakenコア、600Gbpsのイーサネットコア、112GbpsのPAM4トランシーバー、DMA(Direct Memory Access)内蔵PCIe 5.0(CCIXとCXLの両方をサポート)である。これらを統合したことで、既存の14nm/16nm FPGAに比べ、3倍の帯域幅と2倍の演算密度を実現したとする。

XilinxのHigh-End FPGA & ACAPsでプロダクト マーケティングおよびプロダクト マネージメント シニアマネジャーを務めるMike Thompson氏は2020年3月6日にオンラインで行われた日本向けの記者説明会で、「Versal Premiumは、Versal Primeを拡張し、セキュリティ、コネクティビティ、演算性能を高めたもの。Versal Premiumは驚異的なレベルの統合を実現しており、(同等レベルの性能をFPGAで実現するならば)16nmの『Virtex UltraScale+』が22個必要になる。それがVersal Premiumであれば1チップで済む」と語った。

セキュアなネットワーキングを実現

Versal Premiumでは、セキュアなネットワーク構築のための機能を強化している。Xilinxでプロダクト マーケティングおよびマネージメント シニアディレクターであるSumit Shah氏は「通信事業者は、以前はコストへの関心が高かったが、現在はセキュリティへの関心が最も高い」と話す。

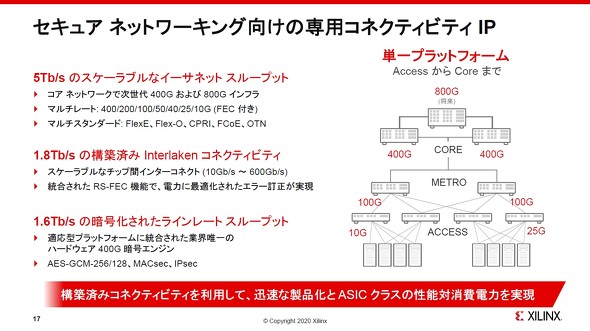

ネットワーキング向けの専用コネクティビティIPとしては、まず、最大5Tbpsのスループットに対応するイーサネットを搭載。FlexE、FlexO、CPRIなど複数の規格をサポートする。Interlakenの接続は標準で1.8Tbpsまで搭載されていて、10G〜600Gbpsのチップ間インターコネクトが可能になっている。さらにThompson氏は、最も重要なポイントとして、暗号化したラインレートを最大1.6Tbpsまで出力できるということを強調した。「これは業界で唯一、ハード化した400Gの暗号化エンジンだ。AES-GCM-256/128の他、MACsec、IPsecもサポートしている」(同氏)

Versal Premiumは、このようにコネクティビティIPがあらかじめ搭載されているため、10G〜25Gのアクセスネットワークから、100G〜200Gのメトロネットワーク、400Gや800Gのコアネットワークまで、1チップでサポートできる。

Copyright © ITmedia, Inc. All Rights Reserved.