「VLSIシンポジウム2020」は初のオンライン開催に:「これからの40年」がテーマ(2/3 ページ)

2020年6月15〜18日(以下、特に記載がない限り全てハワイ時間)に開催される半導体デバイス/回路技術に関する国際会議「VLSIシンポジウム 2020」。本来は米国・ハワイで開催される予定だったが、新型コロナウイルス感染症(COVID-19)の影響で、初のオンライン開催となる。VLSIシンポジウム委員会は2020年5月20日、記者説明会をオンラインで開催し、概要を説明した。

VLSI技術シンポジウム

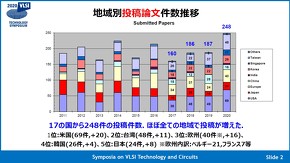

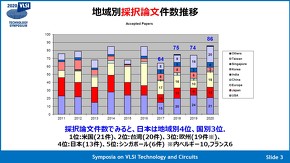

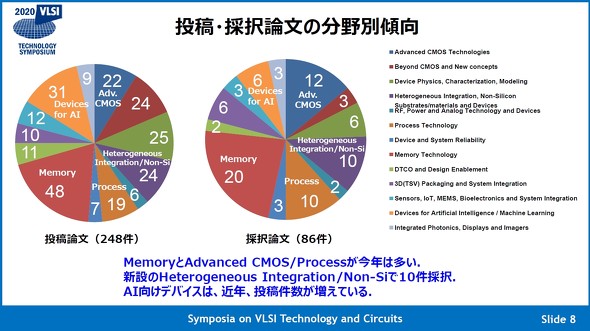

VLSI技術シンポジウムでは、投稿論文数は過去14年で最多となる248件となった。幸いなことに、2020年2月の投稿時点では、COIVD-19の影響をそれほど受けなかったと考えられる。投稿数は、ほぼ全ての地域で増加した。採択論文数は86件で、2019年の74件から増加した。日本からの採択数は13件で、地域別に見ると米国、台湾、欧州に続く4位、国別では米国、台湾に続く3位となっている。

分野別では、投稿、採択ともにメモリ関連が最多となっている。近年は、AIデバイス分野の投稿件数が増えていることも特徴だ。

注目論文

・HBM(High Bandwidth Memory)向けの低温チップ接合、積層技術(TSMC)

量産されている既存のHBMは、DRAMを8層積層しているが、それを12層まで積層できる技術。ロジックダイから最上層のDRAMまでの電気的接合をTSVにより構築した。従来のマイクロバンプ技術に比べて、バンド幅を18〜20%、省電力を8〜15%改善できるとする。

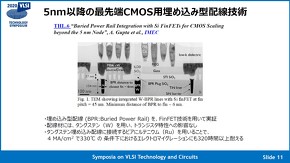

・5nm以降の最先端CMOS用埋め込み型配線技術(imec)

シリコン基板の下にメタル配線を埋め込んで作る埋め込み型配線(BPR:Buried Power Rail)を、FinFET技術を用いて実証した。配線材にはW(タングステン)を用いている。配線を接続するビアにRu(ルテニウム)を用いることで、330℃の条件下におけるエレクトロマイグレーションにも320時間以上耐えるという。

・HPC(High Performance Computing)向け7層ナノシートトランジスタ(CEA-Leti)

ナノシートを7層積層したGAA(Gate All Around) NS(ナノシート)トランジスタ。今までは最大で4層だった。この7層積層のGAA NSトランジスタについて動作検証を行ったところ、2層積層のGAA NSトランジスタに比べて、3倍のドレイン電流(3mA/μm@VDD=1V)を達成した。

・先端CMOSのエアスペーサー形成技術(IBM Research)

先端CMOSにエアスペーサーを導入する技術。ゲート電極とドレイン電極の間にエア(空洞)スペースを作り、誘電率を極限まで落とすことで実効容量を低減できる。実効容量としては15%低減できることを実証しており、これはFinFETを7nmから5nmにスケーリングするよりも優れた効果だとする。

・量子コンピューティング向け 極低温でのトランジスタばらつき評価(CEA-Leti/STMicroelectronics/Institut Neel)

28nm FD-SOI(完全空乏型Silicon on Insulator)プロセスを用いたトランジスタを、100mK(ミリケルビン)の極低温で動作した時のデバイス性能とばらつきの影響を報告。100mKでも高い性能が得られ、IONは1mA以上、IOFFは1fA未満を達成した。

・酸化物トランジスタを用いたReRAMの集積化(東京大学)

3次元ニューラルネットワークの実現に向けた、ReRAMの集積化技術である。IGZOをチャネルとしたアクセストランジスタを用いて、ReRAMセルアレイを3次元に積層する。それによって、インメモリコンピューティングの動作実証に「初めて成功した」(VLSIシンポジウム委員会)点が高い評価を受けているという。

・7nm EUVを用いた、5G/AIを統合したモバイルチップ(Qualcomm Technologies/Samsung Electronics)

Samsung Electronicsの、EUV(極端紫外線)リソグラフィを適用した7nmプロセスで、QualcommのSoC(System on Chip)「Snapdragon 765」を実現した。前世代の8nm FinFETに比べ、20%の性能改善と35%の消費電力削減を達成している。Snapdragon 765は5G(第5世代移動通信)モデムのチップではあるが、ロジックメモリの動作電圧を下げることで、AIエンジンの統合も成功した。

・300mm基板上にGaNとSiトランジスタを形成(Intel)

300mmのSi基板上に、GaNトランジスタ(NMOS)を形成し、その上にウエハーボンディングによてSi CMOSを貼り合わせた。特性を劣化させることなく、両方を動作させた点が評価された。

・65nm CMOSとシリコンフォトニクスで実現するA-Dコンバーター(UC Berkeley/MIT/LBNL/CNSE)

65nm CMOSとシリコンフォトニクスのチップを、銅のTSV(シリコン貫通ビア)で3次元接続したA-Dコンバーター。40dB、あるいは37dB(45GHz入力時)のSNDRを実現することができた。

・In-Al-Zn-Oを用いた縦型トランジスタ(キオクシア)

新規酸化物半導体In-Al-Zn-Oをチャネル材料に用いた、サラウンディングゲート縦型トランジスタの動作実証に成功した。同じ酸化物半導体であるIGZOを用いた場合に比べ、優れた熱安定性(〜420℃)と移動度(12.7cm2/Vs)を実現している。ゲート長も40nmと、微細なゲートで作られていることも特長だ。

・大きなメモリウィンドウを実現する半円筒形状の3D NANDフラッシュ(Macronix International)

ゲート電極を“分断”する半円筒型の3D NAND型フラッシュメモリ素子についての論文。半円筒にすることで、通常のGAA型3D NANDフラッシュ素子に比べてセル面積が32%になり、10万回の書き換え耐性を実現した。

・4重界面垂直磁気トンネル接合(MTJ)の微細化特性(東北大学)

STT-MRAMについての論文。300mmウエハーを用いた独自のPVD技術やエッチング技術で、33nmまで縮小したMTJを作製したのがポイントになる。1011以上という優れたエンデュランス特性を実現したことも特長だ。1Xnmノードまでのスケーラビリティも備えている。

・急冷法で実現した分極を有するAl:HfO2強誘電体薄膜(Hanyang University)

純水で急冷することにより発生した過去最大の残留分極と抗電界を持つAlをドープした、HfO2(Al:HfO2)強誘電体薄膜の作製に成功した。HfO2やAl:HfO2は、次世代の3D NANDフラッシュ向けとして期待されている材料でもある。

Copyright © ITmedia, Inc. All Rights Reserved.