「世界初」SOT-MRAMチップの動作実証に成功、東北大:書き込み60MHz、読み出し90MHzを達成

東北大学国際集積エレクトロニクス研究開発センター(以下、CIES)と同大電気通信研究所は2020年6月15日、スピン軌道トルク型磁気トンネル接合(SOT-MTJ)素子を用いた不揮発性メモリ(SOT-MRAM)チップを試作し、その動作実証に世界で初めて成功した、と発表した。

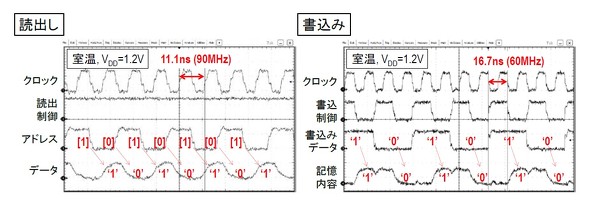

東北大学国際集積エレクトロニクス研究開発センター(以下、CIES)と同大電気通信研究所は2020年6月15日、スピン軌道トルク型磁気トンネル接合(SOT-MTJ)素子を用いた不揮発性メモリ(SOT-MRAM)チップを試作し、その動作実証に世界で初めて成功した、と発表した。メモリセルを3万2768ビット(=4キロバイト)搭載したデュアルポート型SOT-MRAMチップで、無磁場環境下における高速な同時並行動作(書き込み60MHz、読み出し90MHz)を達成。「ICT社会基盤のパラダイムシフトをもたらし、Society5.0を実現するための基盤技術として期待される」としている。

「世界初」のチップ動作実証、実用化へ大きな一歩

トランジスタの微細化に伴う待機電力の増大という半導体メモリの課題解決に向け、内蔵メモリとして情報の保持に電力を必要としない不揮発性メモリの研究開発が加速している。

なかでも、「磁気トンネル接合(MTJ:Magnetic tunnel junction)素子」と呼ばれる、磁石の性質を有する材料で構成された2つの層が薄い絶縁層を挟んだ構造の素子の応用が進められており、その代表的な製品技術として、「STT(Spin-transfer-torque magnetoresistive random accessmemory)-MRAM(スピン注入型磁気抵抗メモリ)」がある。STT-MRAMでは、MTJ素子に直接電流を流すことで、2つの強磁性体のうち片方の強磁性体の磁石の方向を反転させ、デジタル情報の書込みを行う。これはCMOSと混載した際にメモリセルを最も小さくできる方式で、既に混載キャッシュメモリのSRAMやフラッシュメモリの代替用途で量産出荷が進められているという。

ただ、混載キャッシュメモリのSRAMの置き換えとして、モバイル市場だけでなくサーバなどの市場にもMRAMを拡大するためには、その動作速度をナノ秒からサブナノ秒オーダーにまで高速化する必要がある。この課題の解決に向け、同大が進めているのがSOT-MRAMに関する技術開発だ。CIESセンター長、遠藤哲郎氏らのグループは2019年12月、400℃の熱処理耐性と無磁場で350ピコ秒の高速動作、10年間データ保持可能とする熱安定性を実現するSOT素子を作製、さらに開発した素子を用いたメモリ(SOT-MRAM)セルも試作し、10ナノ秒の高速書き込み性能も実証した、と発表している。

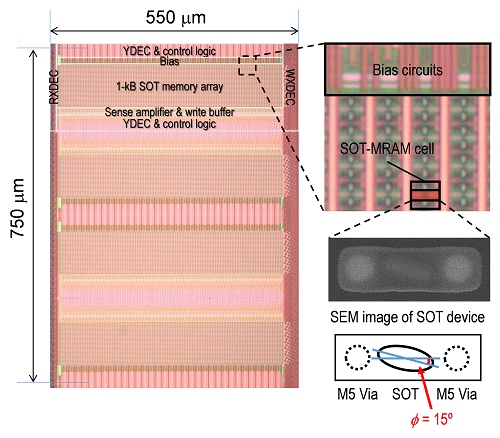

これまでの研究開発は上記の通り、素子レベルや単体メモリセルレベルでの試作、動作実証にとどまっていたが、今回、電気通信研究所教授の羽生貴弘氏、准教授の夏井雅典氏らの研究グループが研究開発してきたSOT-MRAMセルアレイの高速動作を実現する回路技術と、遠藤氏のグループのSOT-MRAMにかかる材料、セル技術および300mmプロセス集積化、製造技術を融合させることで、「SOT-MRAMチップ」の試作および動作実証に成功したとしている。

試作されたメモリチップは、メモリセルを3万2768ビット(=4キロバイト)搭載。書込みと読出しの電流経路が異なるという3端子型SOT-MTJ素子の構造を活用し、MTJ素子を使用したメモリとしては「世界初」となるデュアルポート型を実現しており、無磁場環境下において、書き込み60MHz、読み出し90MHzの同時並行動作を実証した。

同グループは、「今後、さらなる先端MOS技術を用いたSOT-MRAMを開発しSOT素子が有するナノ秒からサブナノ秒オーダーの高速動作を実現することで、広帯域のデータ処理を必要とするFPGAやAI(人工知能)ハードウェアなどへの不揮発性メモリ技術の適用を大きく前進させることにつながる」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東北大学、SOT-MRAMセルの動作実証に成功

東北大学、SOT-MRAMセルの動作実証に成功

東北大学は、400℃の熱処理耐性と無磁場で350ピコ秒の高速動作、10年間データ保持を可能とする熱安定性を実現したスピン軌道トルク(SOT)型磁気トンネル素子の作製に成功した。SOT-MRAMセルとしての動作も確認した。 拡大基調が見え始めたMRAM、鍵はエコシステムと製造技術

拡大基調が見え始めたMRAM、鍵はエコシステムと製造技術

MRAM(磁気抵抗メモリ)の採用が拡大基調に突入しようとしている。ただし、採用がすぐに進むかどうかは、製造技術の進歩と、ディスクリートおよび組み込みMRAMデバイスの技術をサポートするエコシステムの発展の両方にかかっている。 次世代メモリの長所と短所を一覧する

次世代メモリの長所と短所を一覧する

本シリーズの最終回となる今回は、次世代メモリの長所と短所をまとめる。既存のメモリ技術ではDRAM、NANDフラッシュが主流であり、少なくとも今後5年間はその地位が揺らぐことはないだろう。 磁気抵抗メモリ(MRAM)の技術動向と製品動向

磁気抵抗メモリ(MRAM)の技術動向と製品動向

今回は、MRAMの技術開発状況と製品化動向を取り上げる。特に、最近のMRAM開発で注目されている埋め込みメモリについて解説する。 磁気抵抗メモリ(MRAM)の長所と短所

磁気抵抗メモリ(MRAM)の長所と短所

今回から磁気抵抗メモリ(MRAM)について解説する。まずはMRAMの構造と、長所、短所をそれぞれ説明しよう。 次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

次世代メモリ技術の最有力候補はPCMとMRAM、ReRAM

今回は、次世代メモリの立ち位置を再確認した上で、相変化メモリ(PCM)、磁気抵抗メモリ(MRAM)、抵抗変化メモリ(ReRAM)という3つの最有力候補について解説する。