1nmが見えてきたスケーリング 「VLSI 2020」リポート:湯之上隆のナノフォーカス(27)(2/7 ページ)

初のオンライン開催となった「VLSIシンポジウム 2020」から、スケーリング、EUV、3D ICの3つについて最新動向を紹介する。

1nmノードのスケーリング

ことし2020年、TSMCが孔だけでなく配線にもEUV露光装置を使う5nmノード(以下、ノードは省略)のロジック半導体を量産している。また、10月からは3nmのリスク生産を開始し、来年2021年に量産する計画である。そして、2021年のリスク生産を目指して、既に2nmの開発が本格化している。

微細加工の最先端を行くTSMCの状況を考えると、VLSIシンポジウムの発表タイトルに、7nm、5nm、3nmという技術ノードが書かれていても、あまり驚きがない。それよりも、「2nm以降はどうなるのか?」ということに、筆者は注目した。

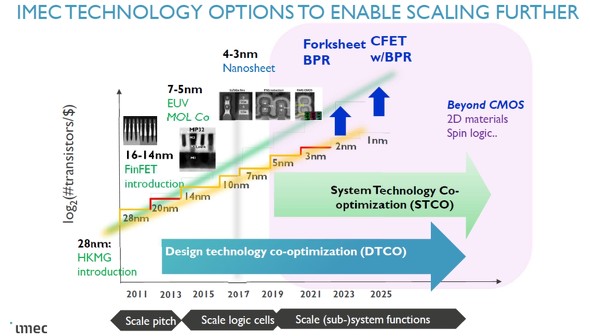

このような中、ベルギーimecのMyung Hee Na氏が、Friday Forumの発表で、1nmまでのロードマップを示した(図5)。このロードマップの縦軸は、対数で示されたトランジスタ当たりのコストであり、横軸はその技術ノードの量産開始年である。この横軸は、TSMCの量産計画とほぼ一致している。

図5:1nmまでのロードマップ 出典:Myung Hee Na, imec, “CMOS and Beyond CMOS Technologies for Edge Intelligence”, VLSI 2020, FF5(クリックで拡大)

このロードマップによれば、28nmでHigh-K/Metalゲートが使われ、16-14nmでFinFETが導入され、7-5nmではEUV露光装置を使い、加えてMiddle of Line(MOL)にCoを使うことになっている。MOLは、トランジスタ(FOEL)と多層配線(BEOL)をつなぐビアで、imecはCoを使うことにしているが、他にもMoやRuなどの選択肢がある。

そして、4-3nmではNanosheet構造のトランジスタが採用される。今回のVLSIシンポジウムでは、7nm、5nm、3nmのトランジスタに関する発表が多数あったが、この辺りの技術ノードでGate All Around(GAA)のNanosheet構造を使うことは、世界の共通認識になっているように感じた。

さらに、2nmでは、Buried Power Rail(BPR、トランジスタの下に電源ラインを埋め込む構造)を持つForksheetなるトランジスタを使い、1nmでは、やはりBPRを採用したComplementary FET(CFET)になるとロードマップに記載されている。

ForksheetからCFETへ

2019年のVLSIシンポジウムでは、imecが5nm、3nm、2nmにCFETを使うという発表を行った(関連記事:「半導体業界のトレンドは「3次元化」が明確に VLSI 2019」)。筆者は、発表者の一人に、「imecは、一体どの技術ノードからCFETを使うつもりなのか?」とメールで質問したところ、「今のところ、imecとしての統一見解はない」という回答を得た。

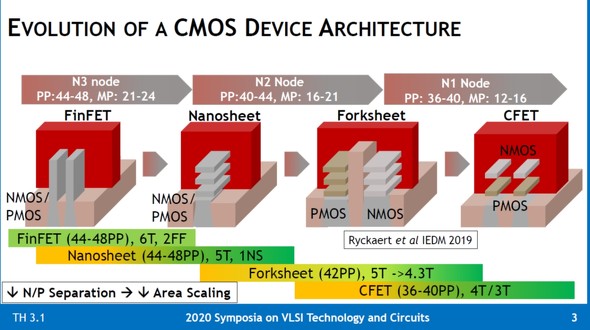

その後、imecは、3nmまではNanosheet、2nmはForksheet、1nmはCFETというロードマップに組織内の共通認識を統一した模様である。というのは、今回のVLSIシンポジウムで、imecの他の発表者、例えば、Sujith Subramanian氏も、上記のロードマップに準拠した発表を行っていたからである(図6)。

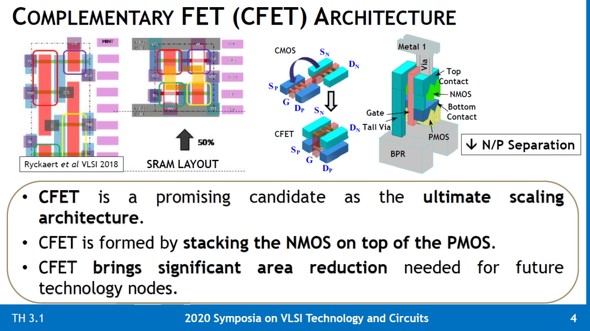

図6:CMOS構造の変化、FinFET→NanoSheet→ForkSheet→CFET 出典:Sujith Subramanian, imec, “First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers”, VLSI 2020, TH3.1(クリックで拡大)

この図は、FinFET、Nanosheet、Forksheet、CFETの構造の変化を非常に分かりやすく示している。FinFETからCFETに至るまで、コンタクト・ポリ・ピッチ(PP)を極力小さくし、nMOSとpMOSをセパレートすることによって、CMOSの面積、そしてSRAMの面積を縮小することを目指している。

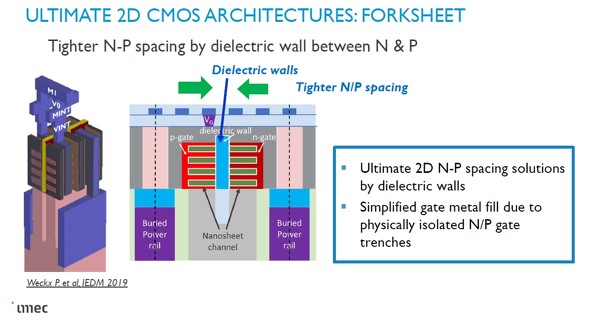

Forksheetは、VLSIシンポジウムでは、今年初めて登場したトランジスタ構造であるが、Nanosheetを形成し、その中間を絶縁膜の壁でセパレートすることにより、nMOSとpMOSをつくり分けている(図7)。nMOSとpMOSのNanosheetを別々につくるよりも工程数が削減できるのかもしれない。

図7:2nmノードを想定しているFORKSHEET 出典:Myung Hee Na, imec, “CMOS and Beyond CMOS Technologies for Edge Intelligence”, VLSI 2020, FF5(クリックで拡大)

そして、1nmでは、nMOSとpMOSを縦に並べるCFETを採用する(図8)。CFETのプロセスフローは非常に複雑であるが、CMOSやSRAMの面積を極めてコンパクトにできることは間違いない。問題は、所望のトランジスタ特性を得ることができるかどうかだが、今後の開発に期待したい。

Copyright © ITmedia, Inc. All Rights Reserved.