1nmが見えてきたスケーリング 「VLSI 2020」リポート:湯之上隆のナノフォーカス(27)(4/7 ページ)

初のオンライン開催となった「VLSIシンポジウム 2020」から、スケーリング、EUV、3D ICの3つについて最新動向を紹介する。

DRAMのスケーリング

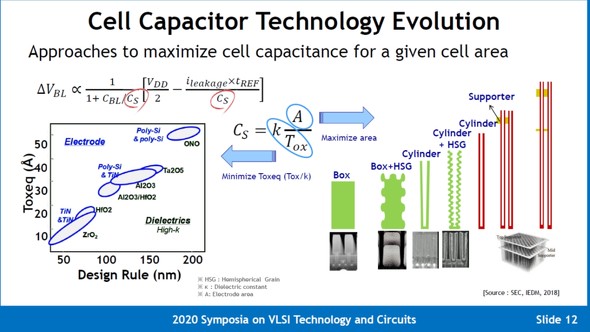

DRAMの開発では、毎回、キャパシターに苦労してきたし、今後もそうなるだろう。Samsung ElectronicsのGwan-Hyeob Koh氏が、DRAMのキャパシターの歴史を図13に示している。DRAMをスケーリングするに当たって、キャパシターに蓄える電荷量をある一定値に保つ必要がある。そのため、キャパシター絶縁膜の誘電率を上げることと、キャパシター面積を確保するための工夫が同時に行われてきた。

図13:DRAMキャパシターの進化 出典:Gwan-Hyeob Koh, Samsung Electronics, “Challenges and Prospects of Memory Scaling”, VLSI 2020, SC1.3(クリックで拡大)

キャパシター絶縁膜としては、SiO2/SiN/SiO2(ONO)、Ta2O5、Al2O3、Al2O3/HfO2、HfO2、そして最近はZrO2になったことが図13の左のグラフから読み取れる。

一方、キャパシター面積を増大させるためには、ピラー構造のポリSi電極の周りにキャパシター絶縁膜を成膜するBox、ポリSi表面に凸凹を形成してTa2O5を形成するBox+HSG(Hemi-spherical grained Poly-Si)、深い孔の中にキャパシター絶縁膜を形成するシリンダ方式、シリンダの内外周部にHSGを形成する方法を経て、その後はただひたすら深い孔を掘ってその内外周部に高誘電率膜を形成するシリンダ方式が採用されている。

注目すべき点は、そのシリンダのアスペクト比(縦横比)があまりにも大きくなりすぎたため、隣り合うシリンダがくっついてしまう不良を防ぐために、サポート(橋桁のようなもの)が形成されるようになったことである。そのサポートは、最近では、2段形成されていることに驚かざるを得ない。

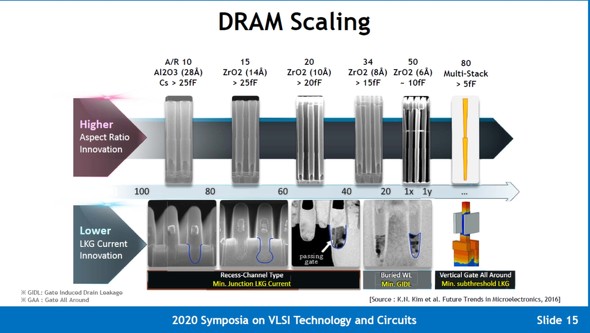

ここまでは、大体理解していたつもりである。従って、この先はどうなるのかを筆者は知りたかった。そのロードマップが、図14に書かれていた。シリンダのアスペクト比は、10、15、20、34、50と次第に大きくなってきていた。現在、最先端の1X、1Y、1Zあたりが、アスペクト比50である。

図14:DRAMのスケーリング 出典:Gwan-Hyeob Koh, Samsung Electronics, “Challenges and Prospects of Memory Scaling”, VLSI 2020, SC1.3(クリックで拡大)

そしてその先は、アスペクト比80となり、そのシリンダは、Multi-Stackで形成されると書かれている。現在、96層以上の3次元NANDフラッシュメモリ(以下、NAND)のメモリホールをSamsung以外が、Multi-Stackで形成している。それと同じように、DRAMのシリンダもMulti-Stackで形成するというのである。

「DRAMのシリンダをMulti-Stackで形成」ということにも驚くのだが、Samsungは128層の3次元NANDをSingle-Stackで形成すると発表している。そのメモリホールのアスペクト比は約80のはずである。同じアスペクト比80の孔の開口について、DRAMはMulti-Stackなのに、3次元NANDはSingle-Stackを採用しようとしている。Samsungの内部でも、技術覇権争いがあるのだろうか?

Copyright © ITmedia, Inc. All Rights Reserved.