1nmが見えてきたスケーリング 「VLSI 2020」リポート:湯之上隆のナノフォーカス(27)(6/7 ページ)

初のオンライン開催となった「VLSIシンポジウム 2020」から、スケーリング、EUV、3D ICの3つについて最新動向を紹介する。

3D ICの加速

スローダウンしながらも、微細化は続いており、今回のVLSIシンポジウムでは、2〜1nmのトランジスタ構造が示された。また、その微細加工のために、EUV露光装置が量産適用され、ASMLはフル稼働でEUVを製造し出荷している。

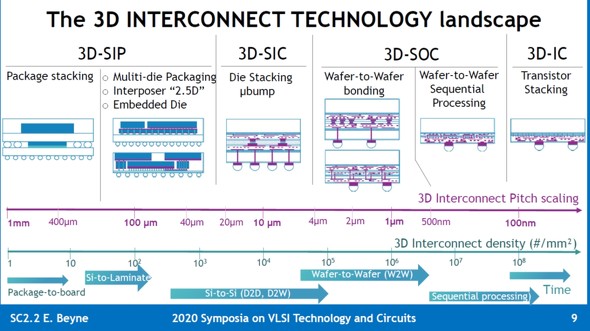

しかし、最先端のシステムや電子機器からの要求はもっと大きく、微細加工を進めながら(More Moore)、それ以上にトランジスタの集積を要求している(More than Moore)。そして、後者のために、さまざまな半導体チップを積層する3D ICの技術が進化している(図21)。

図21:3次元のチップ積層の進化 出典:Eric Beyne, imec, “Heterogeneous System Partitioning and the 3D Interconnect Technology Landscape”, VLSI 2020, SC2.2(クリックで拡大)

パッケージを積層したり、インターポーザを介してチップを並べたりするSiP(System in Package)の次に、マイクロバンプを介してチップを積層する3D SICが登場し、チップを作り込んだウエハーとウエハーを直接ボンディングする3D SOCが実現した。そして、トランジスタをスタックする3D ICが開発されている。

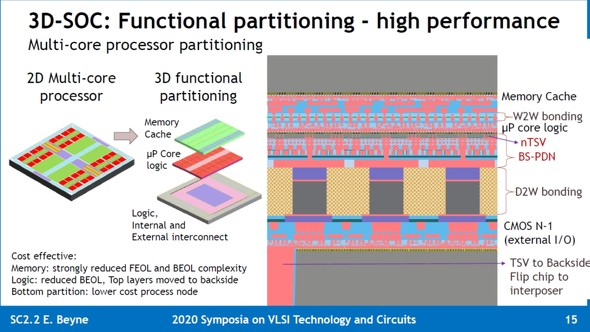

例えば図22では、3D SOCとして、キャッシュメモリとコアになるロジック半導体をマイクロTSV(Through-Silicon Via)でつなぎ、さらに、異なるロジック半導体をボンディングでつないでいる。

図22:3D ICの構造 出典:Eric Beyne, imec, “Heterogeneous System Partitioning and the 3D Interconnect Technology Landscape”, VLSI 2020, SC2.2(クリックで拡大)

もしこれを1チップで製造しようとすると、ロジック半導体とメモリを含んだマスクセットを用意し、べらぼうに長いプロセスフローを構築しなくてはならないだろう。一方、異種半導体をスタックできるのなら、ロジックはロジック、メモリはメモリに特化して製造し、それぞれの良品を接合すればよいことになる。3D SOCを設計するときに、全体最適化(Design Technology Co-Optimization、DECO)が必要になるが、プロセスコストやTAT(Turn Around Time)は、間違いなく3D SOCの方が有利だろう。

TSMCが開発した3D IC

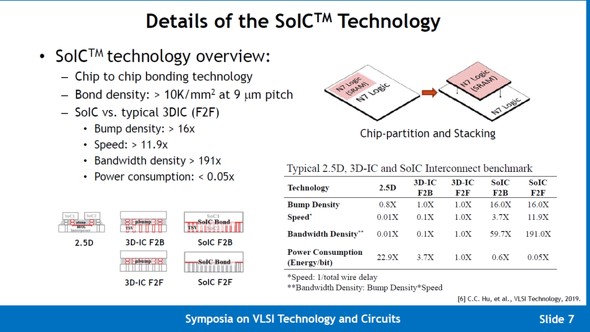

TSMCが開発したImmersion in Memory Compute(ImMC)という3D ICの技術(略してSoICTM)は、コストだけでなく、パフォーマンスも抜群に優れている。

メモリとロジック半導体の一般的な3D IC(F2F:Face to Face)に対して、ベストな3D ICの“SoIC(F2F)”は、バンプ密度が16倍、スピードが11.9倍、バンド幅密度が191倍、1ビット当たりの消費電力は何と0.05倍になるのである(図23)。

図23:TSMCのSoICTMの効果 出典:C.T. Wang, TSMC, “Immersion in Memory Compute (ImMC) Technology”, VLSI 2020, TH1.5

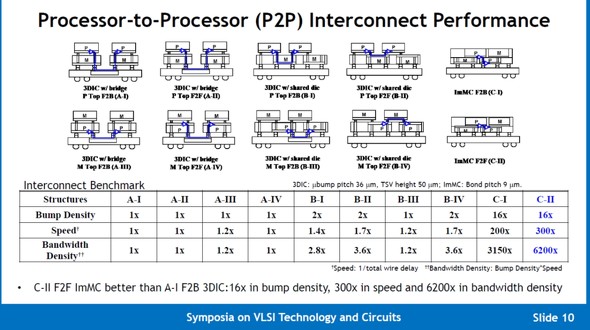

さらに、プロセッサ2個、メモリ2個を、3次元的に接続する場合、どのような積層方法がベスト化を考えてみよう(図24)。ベストパフォーマンスを求めるなら、なるべく電子の移動距離を小さくするように設計するべきである。このように、システムの最適化を考えて設計することを、System Technology Co-Optimization(STCO)と呼ぶ。

図24:プロセッサとプロセッサの接続のパフォーマンス 出典:C.T. Wang, TSMC, “Immersion in Memory Compute (ImMC) Technology”, VLSI 2020, TH1.5(クリックで拡大)

A-I構造を基準として、最も電子の移動距離が小さなC-II構造を採用した場合、バンプ密度は16倍になり、スピードは300倍、バンド幅密度が6200倍にもなる。

Copyright © ITmedia, Inc. All Rights Reserved.