推論を加速する光コンピューティングプロセッサ:NVIDIA Ampere A100をしのぐ?

米国のLightmatterは、2020年8月16日〜18日にバーチャルで開催された「Hot Chips 32」でテストチップを発表した。同社は米マサチューセッツ工科大学(MIT)のスピンアウト企業で、AI(人工知能)アクセラレーション向けオプティカルコンピューティングプロセッサの開発を手掛ける。

米スタートアップが開発

米国のLightmatterは、2020年8月16〜18日にバーチャルで開催された「Hot Chips 32」でテストチップを発表した。同社は米マサチューセッツ工科大学(MIT)のスピンアウト企業で、AI(人工知能)アクセラレーション向けオプティカルコンピューティングプロセッサの開発を手掛ける。

Lightmatterが発表したプロセッサは、シリコンフォトニクスとMEMS技術を使用し、ミリワットクラスのレーザー光源で駆動する半導体で、光速で行列ベクトル乗算を実行する。最新のGPUを含むトランジスタベースの半導体と比べて桁違いに高速な演算処理が可能で、消費電力も非常に少ない。

Lightmatterがこのテストチップを披露した目的は、プロセッサ設計へのアプローチが確かなものであることを証明することだ。同社は、AI推論のワークロードに対応したオプティカルコンピューティング(シリコンフォトニクス)チップを最初に発表した企業のうちの1社である。

同社は2021年秋に、同社初となる商用製品を発売する予定である。今回発表したテストチップの後継機種をベースにしたオプティカルコンピューティングチップを搭載するPCIe(PCI Express)カードで、データセンターのAI推論ワークロードに向ける。

シリコンフォトニクス技術(シリコンチップを介して光を伝播させる技術)の進歩によって、トランジスタベースの従来のエレクトロニクスとは全く異なる方法でMAC演算を実行できる複雑なオンチップ構造が実現しつつある。トランジスタベースのチップがデナードスケーリングの限界に達して以降、単位面積当たりの電力損失が増加しており、冷却技術の実質的な限界によって、サイズが大きなチップに対応できなくなっている。そこで、エネルギー効率に優れた別の技術に期待が寄せられている。

LightmatterのCEO(最高経営責任者)を務めるNick Harris氏は、Hot Chipsの前にEE Timesが行ったインタビューで、「オプティカルコンピューティングは、これまでとは異なるルールセットを使用したスケーリングによって、高速かつ低エネルギーな処理性能を実現できる」と述べている。

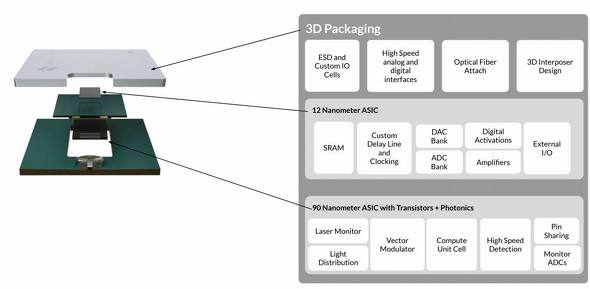

Lightmatterのチップは、2つのダイを垂直に積層したものだ。上部のダイは12nmプロセスを適用したASICで、メモリと、下部のダイである90nmのシリコンフォトニクスダイを制御する回路が搭載されている。どちらのダイも、標準的なCMOSプロセスを用いてGLOBALFOUNDRIESで製造されている。

フォトニクスプロセッサには64×64のフォトニクスベクトル演算器が集積されていて、データはチップ内部を200ピコ秒以内で伝搬するという。コンピュータエンジンは、50mWのレーザーで駆動される。

AIデータセンターのエネルギー消費が20分の1に

正確にはどれくらいの速度と省エネを実現できるのだろうか。

Harris氏は、「既存のAIデータセンターの場合、エネルギー消費を20分の1に削減し、物理的なフットプリントを5分の1に縮小することができる。これは、当社が開発している第1世代のチップを使用した場合の成果であり、今後のロードマップでさらなる改善が期待できる」と述べている。

同氏は、「このテストチップは、同技術のデモ用に開発したもので、ベンチマークで好成績を出すことを目的としたものではない」と強調する一方で、「このデモ機は実際の用途において、NVIDIAの次世代ハイエンドGPUである『Ampere A100』に勝る性能を発揮する」と断言した。同氏によれば、Lightmatterのチップは、Ampere A100に比べ、20倍のエネルギー効率を実現し、BERTやResnet-50の推論といったワークロードで少なくとも5倍のスループットを達成したという。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

情報社会の大いなる“裏方”、光伝送技術

情報社会の大いなる“裏方”、光伝送技術

地球上に、網の目のごとく張り巡らされている光ファイバーネットワークなど、光通信は、われわれの生活に身近な技術である。だが、専門外の技術者にとっては「難しそうで近寄りがたい分野」だと思われているようだ。この連載では、おさえておきたい光伝送技術の基礎と現在のトレンドを分かりやすく解説していく。 光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

今回は、“Beyond 400G”に向けた議論とともに、Pluggableにおける3つの問題点を紹介する。 シリコンフォトニクスとは何か

シリコンフォトニクスとは何か

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。 シリコンフォトニクスの技術開発ロードマップ

シリコンフォトニクスの技術開発ロードマップ

今回は、シリコンフォトニクスの技術開発ロードマップを解説する。シリコンフォトニクスの性能向上とコストを、16/14nmから5nm、3nmの技術ノードに沿って見ていこう。 電気通信と光通信の境界

電気通信と光通信の境界

データセンターで信号伝送を担うのは、銅ケーブル(電気通信)と光ファイバーケーブル(光ファイバー通信)だ。今回は、この2つにおける通信速度と通信距離の関係や、光ネットワークの帯域を向上する上で鍵となる技術を解説する。