ムーア則の維持に貢献する配線技術:福田昭のデバイス通信(281) Intelが語るオンチップの多層配線技術(2)

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。

性能とコスト、製造スループット、製造歩留まりを左右

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。3つの共通テーマとは、「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」「SC2:Heterogeneous Integration - To Boldly Go Where No Moore Has Gone Before(ヘテロ集積化-果敢に進め、ムーアが行ったことのない場所へ)」「SC3:Trends and Advancements in Circuit Design(回路設計の動向と進化)」である。蛇足だが、SC2のタイトルは、SF映画「スター・トレック」の有名なフレーズ「to boldly go where no one has gone before(誰も行ったことのない場所へ果敢に進め)」のオマージュだろう。

話題を戻そう。共通テーマ「ロジックとメモリのスケーリングの将来」では、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」と題する講演が非常に興味深かかった。そこで、講演の概要を前回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回では、講演のアウトライン(目次)や配線技術の動向などを述べた。今回は、ムーアの法則と配線技術の関わりをご説明する。

配線技術(相互接続技術)は、半導体チップにさまざまな影響を与える。チップの性能とコスト、製造スループット、製造歩留まりなどを左右する。

現世代の技術ノードから次世代の技術ノードに移行するとき、配線技術(相互接続技術)には以下のような項目が求められる。すなわちローカル相互接続の微細化、性能の向上、妥当なコスト、新しい機能(MIMキャパシターや配線工程で作るメモリやデバイスなど)、である。これらの要求項目を満たすことが、ムーアの法則の維持につながる。

サブトラクティブ法や低誘電率絶縁材料などの将来技術に期待

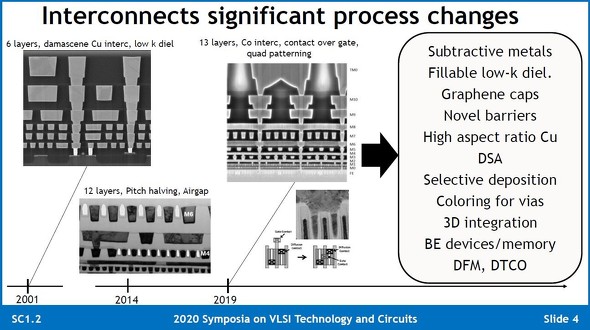

前回でも述べたように、配線技術はこの20年に大きく変化した。この先にも大きな変化が予想される。例えばこれまでの配線製造にはデュアルダマシン法が使われてきた。これがサブトラクティブ法に置き換わる可能性がある。サブトラクティブ法を採用すると、配線抵抗が大きく下がる。

低誘電率の絶縁材料も将来技術の有力候補である。層間絶縁膜として使えれば、配線容量(静電容量)の増加を抑えられる。

このほか、グラフェンをキャップ層に導入することによる配線抵抗の低減、新しいバリア材料(薄いバリア材料)、高アスペクト比の銅(Cu)配線、誘導自己組織化(DSA:Directed Self Assembly)による微細パターンの形成、選択的な成膜、ビア群の区分け(カラーリング)、3次元集積化、バックエンド(多層金属配線)工程を利用したデバイスとメモリの製造、製造容易化設計(DFM:Design for Manufacturability)、設計と製造の同時最適化(DTCO:Design Technology Co-Optimization)、にも期待がかかる。

これらの要素技術のいくつかは本シリーズで後ほど、もう少し詳しく説明したい。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

接合材料に対する要求項目のランキング

接合材料に対する要求項目のランキング

ロードマップ第6章「実装設備」の第4節「実装技術動向」を説明するシリーズ。今回は、「接合材料」に対するユーザーの要望を調査した結果を紹介する。 実装設備が対応すべきプリント配線板と部品供給方式のロードマップ

実装設備が対応すべきプリント配線板と部品供給方式のロードマップ

引き続き、「実装技術動向」を紹介する。今回は、実装設備が対応すべき、プリント配線板と部品供給方式のロードマップについて解説する。 ベアチップ/フリップチップを高い精度で装着

ベアチップ/フリップチップを高い精度で装着

実装設備に要求する項目のアンケート結果を紹介するシリーズ。今回は「ベアチップ/フリップチップボンダ」に対する要求を説明する。 重要さを増す検査機からのフィードバック

重要さを増す検査機からのフィードバック

引き続き、実装設備に要求する項目のアンケート結果を紹介する。今回は、「検査機」に対する要求と対策を取り上げる。 高速・高精度・低コストの実装工程を支える設備と材料

高速・高精度・低コストの実装工程を支える設備と材料

第6章「実装設備」の概要を説明する。まずは表面実装の設備と材料を取り上げる。 HDD大手SeagateとWDの2020会計年度業績、売り上げはいずれも約1%増に

HDD大手SeagateとWDの2020会計年度業績、売り上げはいずれも約1%増に

今回は、Seagate TechnologyとWestern Digital(WD)の2020会計年度の業績を紹介しよう。