Samsung偺EUV揔梡D1z悽戙偺DRAM傪暘愅丗TechInsights

Samsung Electronics乮埲壓丄Samsung乯偑偮偄偵丄偙偙悢僇寧偵傢偨傝懸朷偝傟偰偄偨丄EUV乮嬌抂巼奜慄乯儕僜僌儔僼傿媄弍傪摫擖偟偨乽D1z乿僾儘僙僗偺DRAM偺検嶻傪奐巒偟偨丅摨幮偼2020擭弶摢偵丄乽嬈奅弶乿乮摨幮乯偲側傞ArF塼怹乮ArF-i丗ArF immersion乯儀乕僗偺D1z DRAM偲丄EUV儕僜僌儔僼傿乮EUVL乯揔梡偺D1z DRAM偺椉曽傪奐敪偡傞偲敪昞偟偰偄偨丅

EUV揔梡乽D1z乿悽戙偺DRAM

丂Samsung Electronics乮埲壓丄Samsung乯偑偮偄偵丄偙偙悢僇寧偵傢偨傝懸朷偝傟偰偄偨丄EUV乮嬌抂巼奜慄乯儕僜僌儔僼傿媄弍傪摫擖偟偨乽D1z乿僾儘僙僗偺DRAM偺検嶻傪奐巒偟偨丅摨幮偼2020擭弶摢偵丄乽嬈奅弶乿乮摨幮乯偲側傞ArF塼怹乮ArF-i丗ArF immersion乯儀乕僗偺D1z DRAM偲丄EUV儕僜僌儔僼傿乮EUVL乯揔梡偺D1z DRAM偺椉曽傪奐敪偡傞偲敪昞偟偰偄偨丅TechInsights偼丄Samsung偺嵟怴偐偮嵟愭抂偺D1z DRAM僨僶僀僗傪幚嵺偵尒偰妋偐傔丄偦偺揔梡媄弍偵娭偡傞徻嵶傪妋擣偡傞偙偲偑偱偒丄旕忢偵嫽暠偟偰偄傞偲偙傠偩丅

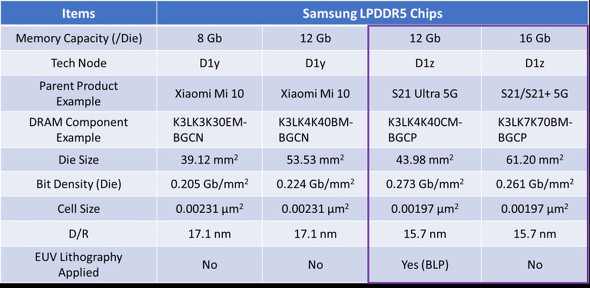

丂Samsung偼崱夞丄D1z僾儘僙僗偺8G價僢僩DDR4 DRAM偲丄D1z偺12G價僢僩LPDDR5 DRAM丄16G價僢僩LPDDR5 DRAM傪奐敪偟偨丅偄偢傟傕崅惈擻壔傪幚尰偟偰偄傞丅偙偺偆偪12G價僢僩偲16G價僢僩偺LPDDR5偼丄摨幮偑2021擭1寧偵敪昞偟偨偽偐傝偺嵟怴僗儅乕僩僼僅儞乽Galaxy S21 5G乿僔儕乕僘乽S21 5G乿偲乽S21+ 5G乿乽S21 Ultra 5G乿偵搵嵹偝傟偰偄傞偙偲偑暘偐偭偨丅

丂12G價僢僩LPDDR5僠僢僾偼丄Galaxy S21 Ultra 5G乮宆斣丗SM-G998B/DS乯偺12G價僢僩RAM偵搵嵹偝傟偰偄傞偑丄16G價僢僩LPDDR5僠僢僾偼丄S21 5G偲S21+ 5G偺8G價僢僩 RAM偵搵嵹偝傟偰偄傞傛偆偩丅

丂傑偨丄D1z僾儘僙僗媄弍偺惗嶻岠棪偵娭偟偰偼丄媽悽戙偺乽D1y乿僾儘僙僗傪梡偄偨12G價僢僩昳偲斾傋傞偲丄D1z僾儘僙僗偺12G價僢僩LPDDR5 DRAM偺曽偑15亾埲忋崅偄偲偄偆丅愝寁儖乕儖乮D/R乯偼丄D1y悽戙偺17.1nm偐傜丄D1z偱偼15.7nm傑偱弅彫偟偰偄傞丅僟僀僒僀僘偵偮偄偰傕丄D1y偺帪偼53.53mm2偩偭偨偑丄D1z偱偼43.98mm2偲丄栺18亾偺弅彫傪幚尰偟偰偄傞乮昞1乯丅

丂EUV傪揔梡偟偨D1z媄弍偱惢憿偟偨12G價僢僩LPDDR5 DRAM偵偼丄乽K4L2E165YC乿偲崗報偝傟偰偄傞丅堦曽丄16G價僢僩LPDDR5 DRAM僠僢僾偵偼乽K4L6E165YB乿偲崗報偝傟偰偄偰丄偙偪傜偺D1z僾儘僙僗偵偼EUV偼揔梡偝傟偰偄側偄丅

丂Samsung偼嫲傜偔丄傑偢ArF-i偍傛傃EUV偺椉曽傪儀乕僗偲偟偨SNLP乮Storage Node Landing Pad乯/BLP乮Bit Line Pad乯儕僜僌儔僼傿傪揔梡偟偰D1z LPDDR5惢昳傪奐敪偟丄偦偟偰尰嵼丄慡偰偺D1z LPDDR5惢昳偵EUV SNLP/BLP儕僜僌儔僼傿傪揔梡偡傞傛偆偵側偭偨偺偩傠偆丅

丂Samsung偼2019擭屻敿偵丄D1x EUV儕僜僌儔僼傿傪揔梡偟偨僒儞僾儖儌僕儏乕儖傪100枩屄弌壸偟偨丅D1z僠僢僾偺惢憿偼丄娯崙僉儑儞僊僪乮嫗婔摴乯偺僺儑儞僥僋乮暯戲乯偵偁傞戞2惢憿儔僀儞偱峴傢傟傞傛偆偩丅

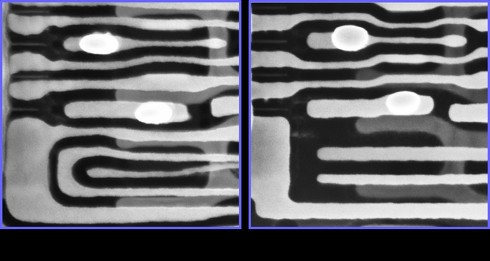

丂摨幮偼丄D1z 12G價僢僩LPDDR5僨僶僀僗偺DRAM僾儘僙僗僀儞僥僌儗乕僔儑儞偵娭偟偰偼丄EUV儕僜僌儔僼傿媄弍偺揔梡傪丄SNLP乮SNLP on call array乯/BLP乮BLP on S/A乯偺1偮偺儅僗僋偩偗偵尷掕偟偰偄傞丅CD乮尷奅悺朄乛僺僢僠乯偼栺40nm丄S/A乮僙儞僗傾儞僾夞楬乯僄儕傾偺BLP儔僀儞暆偼13.5nm偱偁傞丅

丂恾1偺揹巕尠旝嬀幨恀偼丄Samsung偺S/A BLP僷僞乕儞偵偮偄偰丄ArF-i儀乕僗偺儕僜僌儔僼傿傪揔梡偟偨D1z 16G價僢僩LPDDR5僟僀偲丄EUV儕僜僌儔僼傿揔梡偺D1z 12G價僢僩LPDDR5僟僀傪斾妑偟偨傕偺偩丅EUV儕僜僌儔僼傿傪揔梡偡傞偙偲偵傛傝丄S/A僄儕傾偺BLP偺LER乮Line Edge Roughness乯傗丄僽儕僢僕乛抁棈側偳傪掅尭偱偒傞偲偄偊傞偩傠偆丅

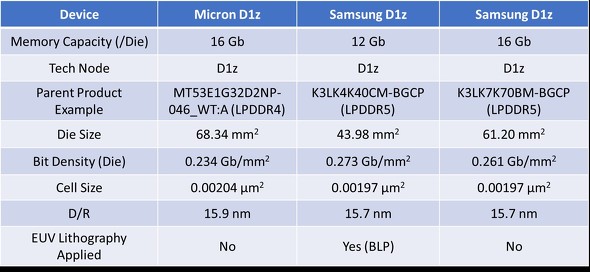

丂傑偨丄嫞崌偺Micron Technology偺D1z僙儖愝寁偲斾妑偟偨応崌丄僙儖僒僀僘偵娭偟偰偼丄Samsung偑0.00197兪m2偱Micron偑0.00204兪m2丄D/R偵偮偄偰偼Samsung偑15.7nm偱Micron偑15.9nm偲丄Samsung偑傛傝彫宆壔偟偰偄傞偙偲偑暘偐傞丅Micron偼丄D1z惢昳偺慡偰偺僼僅僩儅僗僋岺掱偱ArF-i儀乕僗偺儕僜僌儔僼傿傪揔梡偟偰偄傞偑丄摉柺偺娫丄D1兛乛D1兝側偳偵偼EUV儕僜僌儔僼傿傪揔梡偟側偄梊掕偩偲偟偰偄傞乮昞2乯丅

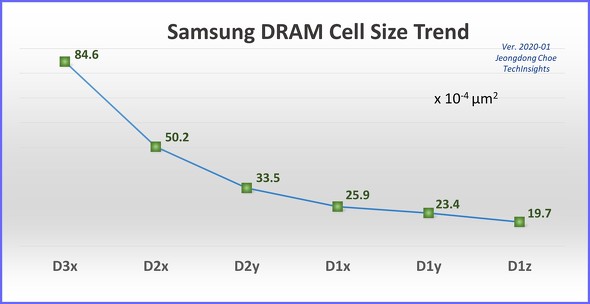

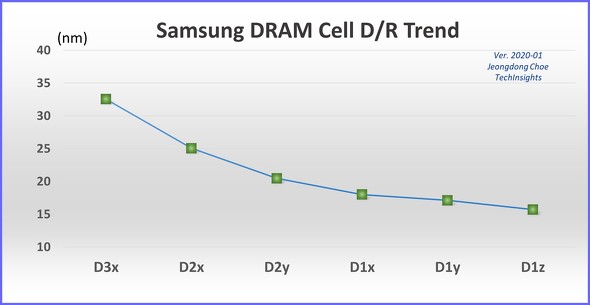

丂恾2偍傛傃恾3偼偦傟偧傟丄Samsung偺D3x偐傜D1z傑偱偺DRAM偺僙儖僒僀僘偲D/R偵娭偡傞摦岦傪帵偟偰偄傞丅嬤擭丄DRAM偺僙儖僒僀僘偲D/R偺弅彫幚尰偼傑偡傑偡崲擄偵側偭偰偒偰偄傞偑丄Samsung偼D1z偺D/R傪丄D1y偲斾傋偰8.2亾尭偲側傞15.7nm偵弅彫偡傞偙偲偵惉岟偟偨丅

丂Samsung偼丄2021擭偵敪昞傪梊掕偟偰偄傞D1兛傗丄2022擭偺D1兝側偳偺師悽戙DRAM偱傕丄堷偒懕偒EUVL岺掱傪憹傗偟偰偄偔梊掕偩偲偄偆丅

亂東栿丗揷拞棷旤丄曇廤丗EE Times Japan亃

Copyright © ITmedia, Inc. All Rights Reserved.

娭楢婰帠

SK hynix偺怴岺応乽M16乿偑姰惉丄1兛nm偺DRAM惗嶻傊

SK hynix偺怴岺応乽M16乿偑姰惉丄1兛nm偺DRAM惗嶻傊

SK hynix偼2020擭2寧1擔乮娯崙帪娫乯丄娯崙丒嫗婨摴偺棙愳乮僀僠儑儞乯巗偵寶愝偟偨怴偨側岺応乽M16乿偺棊惉幃傪峴偭偨丅偙偺怴巤愝偼儊儌儕僨僶僀僗偺惗嶻偵巊傢傟傞梊掕偱丄傑偢偼1兛乮傾儖僼傽乯nm悽戙乮10nm僾儘僙僗乯傪揔梡偡傞DRAM偺惗嶻偐傜奐巒偡傞丅検嶻奐巒偼2021擭屻敿傪尒崬傫偱偄傞丅 NXP傗Infineon偑僥僉僒僗偺掆揹偱惗嶻傪掆巭

NXP傗Infineon偑僥僉僒僗偺掆揹偱惗嶻傪掆巭

暷崙偺庡梫側僄僱儖僊乕嫙媼抧堟偱偁傞僥僉僒僗廈偱偺撍慠偺姦攇偑掆揹傪堷偒婲偙偟偨偙偲傪庴偗偰丄摨廈偵偁傞Samsung Electronics乮埲壓丄Samsung乯丄NXP Semiconductros乮埲壓丄NXP乯丄Infineon Technologies乮埲壓丄Infineon乯偺岺応偑憖嬈傪掆巭偟偨丅 3偮偺媄弍偱崅枾搙壔丄Micron偺176憌3D NAND

3偮偺媄弍偱崅枾搙壔丄Micron偺176憌3D NAND

Micron Technology乮埲壓丄Micron乯偼2020擭11寧18擔丄擔杮偺儊僨傿傾岦偗偵丄摨擭11寧9擔乮暷崙帪娫乯偵敪昞偟偨176憌偺3D NAND宆僼儔僢僔儏儊儌儕乮埲壓丄176憌3D NAND乯偺愢柧夛傪峴偭偨丅 僐儘僫壭偱傕岲挷傪堐帩偡傞敿摫懱儊儌儕巗応

僐儘僫壭偱傕岲挷傪堐帩偡傞敿摫懱儊儌儕巗応

崱夞偐傜丄2020擭11寧偵僶乕僠儍儖偱奐嵜偝傟偨乽僼儔僢僔儏儊儌儕僒儈僢僩乮FMS丗Flash Memory Summit乯乿偺島墘傪徯夘偡傞丅傑偢偼丄敿摫懱儊儌儕偺傾僫儕僗僩Jim Handy巵偵傛傞島墘乽Annual Flash Update - The Pandemic's Impact乮僼儔僢僔儏儊儌儕偺擭師傾僢僾僨乕僩-僷儞僨儈僢僋偺塭嬁乯乿偺梫巪傪曬崘偟偨偄丅 Samsung夛挿惱嫀丄晜偐傃忋偑偭偨敿摫懱嬈奅乬3執恖乭偺堄奜側嫟捠揰

Samsung夛挿惱嫀丄晜偐傃忋偑偭偨敿摫懱嬈奅乬3執恖乭偺堄奜側嫟捠揰

Samsung Electronics偺棝寬辘乮僀丒僑儞僸乯夛挿偑2020擭10寧25擔偵巰嫀偟偨丅摨巵偺宱楌傪偁傜偨傔偰挷傋偰偄偨昅幰偼丄敿摫懱嬈奅偺乬3恖偺執恖乭偵娭偡傞丄堄奜側嫟捠揰傪尒偮偗偨丅偦偺嫟捠揰傪岅傝偮偮丄Samsung偺尰忬偲壽戣傪夝愢偟偨偄丅