Siインターポーザを樹脂基板に変更した低コスト版の「CoWoS」:福田昭のデバイス通信(337) TSMCが開発してきた最先端パッケージング技術(10)(1/2 ページ)

今回からは「CoWoS」の派生品である「CoWoS_R(RDL Interposer)」と「CoWoS_L(Local Silicon Interconnect + RDL Interposer)」の概要を解説する。

Siインターポーザの存在が「CoWoS」のコストを押し上げる

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」がことし(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

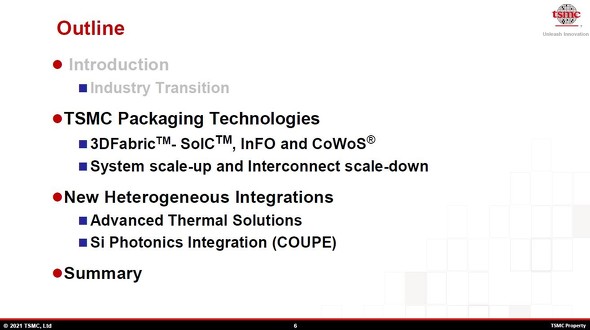

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

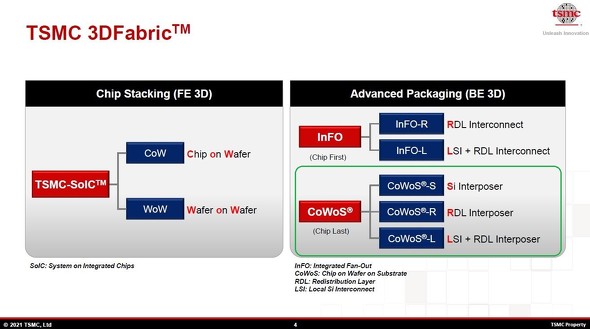

本シリーズの第7回から、高性能コンピューティング(HPC)向けの広帯域高密度パッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」の歴史と最新状況を説明してきた。第9回(前回)まではインターポーザ(中間基板)にSi(シリコン)基板を使う「CoWoS」(現在の名称は「CoWoS_S」)を取り上げた。

今回からは「CoWoS」の派生品である「CoWoS_R(RDL Interposer)」と「CoWoS_L(Local Silicon Interconnect + RDL Interposer)」の概要を解説する。いずれもインターポーザの材料を高価なシリコン(Si)ではなく、安価な樹脂に変更したパッケージング技術だ。本シリーズの第7回〜第9回でも述べたように、世代ごとにSiインターポーザは大型化しており、パッケージのコストを上昇させてきた。高価なシリコン基板をなるべく使わずに、性能を維持するインターポーザが求められる。

Copyright © ITmedia, Inc. All Rights Reserved.